#### **APPLICATION NOTE**

# Scan conversion using the SAA4998 (FALCONIC-EM)

Version 1

AN10233

#### **Abstract**

This application note describes the scan converter module MK14-EM. 50 or 60 Hz video input signals are converted to progressive scan or 100..120 Hz (scan rate doubling,  $2f_H$  and  $2f_V$ ). A software solution permits conversion from 50 Hz to 60 Hz or 75 Hz also, with the horizontal frequency being doubled ( $2f_H$ ).

The module offers various analog inputs as well as a digital ITU-656 interface. Two color decoders permit dual-channel display as double-window or picture-in-picture. The Y-U-V output is analog again.

The ICs used on the board and described in this application note are the color decoder SAA7118, the scan converter SAA4979 and the motion compensation IC with embedded memories, the SAA4998. The memories in the SAA4998 either serve as field or frame memory for motion compensation, or one or both of them can be switched as buffer memory to synchronize the second input channel.

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system, provided the system conforms to the I<sup>2</sup>C specifications defined by Philips.

#### © Philips Electronics N.V. 2003

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copy-right owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

#### **APPLICATION NOTE**

# Scan conversion using the SAA4998 (FALCONIC-EM)

AN10233

Author:

Heinrich Waterholter BL-MTS, S&A Hamburg, Germany

#### **Keywords**

SAA4998, SAA4979, SAA7118,

motion compensation, motion estimation, natural motion

DNR (dynamic noise reduction),

EDDI, edge dependent deinterlacing,

peaking

DCTI

Date: April 30, 2003

Application Note AN10233

#### **Summary**

The MK14-EM Improved Picture Quality (IPQ) module is a scan converter intended to convert TV scan rates of 50 / 60 Hz interlace to 50 / 60 Hz progressive, 75 / 90 Hz interlace or 100 / 120 Hz interlace. All modes are motion compensated. This feature eliminates motion judder which occurs whenever the source movement rate is different from the display rate.

Compared to previous Philips scan converter modules the MK14-EM employs the SAA4998 which is a motion compensation IC with embedded field memories. The memories serve as background field or frame memory for the motion compensation process, but can also be configured as buffer memories for the second simultaneous display channel. In this way the SAA4998 saves four external memories and therefore reduced chip count considerably.

An additional feature compared to previous motion compensation ICs is EDDI (edge dependent deinterlacing). This function analyzes the progressive output signal of the standard deinterlacer and in case of staircases along an edge replaces pixels to generate a smooth edge.

The application note describes the ICs and their picture improvement functions, gives details on circuit diagrams and layout of the board and supplies a register table for control by I<sup>2</sup>C bus.

| Scan conversion using the | SAA4998   |

|---------------------------|-----------|

| (FALCONIC-EM)             | Version ' |

# Application Note AN10233

#### **Table of Contents**

| 1. | Introdu                                                                             | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 10                                                                                                                         |

|----|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 2. | Featur                                                                              | es of IPQ modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 11                                                                                                                         |

| 3. | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12 | Reasons for scan conversion Scan rate doubling Field repetition and frame repetition Video mode and movie mode Line flicker reduction (LFR) Display of moving objects 2:2 and 3:2 pull-down movie modes Motion compensation in movie mode Progressive scan 75 Hz interlace Conversion from 50 Hz to 60 Hz Double clock system                                                                                                                                                                                                                                                                                                                       | . 13<br>. 14<br>. 14<br>. 16<br>. 16<br>. 18<br>. 20<br>. 20                                                                 |

| 4. | 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                                              | Digital processing at 1f <sub>H</sub> level 4.1.1 ITU-656 decoder 4.1.2 Inputs 4.1.3 Double window and picture-in-picture processing 4.1.4 Black bar detector 4.1.5 Dynamic noise reduction 4.1.6 Noise estimator 3.5 MBit field memory Digital processing at 2f <sub>H</sub> level 4.3.1 Sample rate conversion 4.3.2 Expansion Port 4.3.3 Horizontal Zoom, Panorama 4.3.4 Digital Color Transient Improvement (DCTI) 4.3.5 Y horizontal smart peaking 4.3.6 Non-linear phase filter 4.3.7 Post processing: borders, frames and blanking Triple 10-bit digital-to-analog conversion Microcontroller Memory controller Line locked clock generation | . 25<br>. 25<br>. 28<br>. 29<br>. 30<br>. 31<br>. 33<br>. 34<br>. 36<br>. 36<br>. 38<br>. 38<br>. 47<br>. 49<br>. 51<br>. 54 |

| 5. | <b>Functi</b> 5.1 5.2                                                               | Problems in motion portrayal with picture rate conversion  Motion estimation and compensation for luminance  5.2.1 Multi port RAM (MPR)  5.2.2 Motion estimator  5.2.3 Temporal prediction memory (TPM)  5.2.4 Deinterlacer  5.2.5 Upconverter  Vector splitter                                                                                                                                                                                                                                                                                                                                                                                     | . 58<br>. 59<br>. 59<br>. 61<br>. 64<br>. 65                                                                                 |

|     | an co                                  | Application Note                                                                                                                                              |            |         |

|-----|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|

| (F  | ALCC                                   | ONIC-EM)                                                                                                                                                      | Version 1  | AN10233 |

|     | 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | Film mode detected Vertical Peaking and Zoom. Chrominance processing. Memory configuration 100 Hz progressive display. Dynamic Noise Reduction (E             | or         |         |

| 6.  | 6.1<br>6.2<br>6.3                      | The SAA7118 Functional blocks Video acquisition Video decoder . Component video Video scaler Vertical blanking i Audio clock generation bigital I/O interface | processing |         |

| 7.  | <b>Availa</b> 7.1 7.2                  | The IPQ module MK14-EM.                                                                                                                                       |            |         |

| 8.  | <b>Applic</b> 8.1 8.2 8.3              | Motion compensation in a TV Motion compensation in a DV                                                                                                       | / set      |         |

| 9.  | 9.1<br>9.2<br>9.3<br>9.4               | General description                                                                                                                                           |            |         |

| 10. | <b>I2C reg</b><br>10.1<br>10.2         | Write registers                                                                                                                                               | on 4.4)    |         |

| 11. | Appen<br>11.1                          |                                                                                                                                                               |            |         |

| Scan conversion u | using the SAA4998 |

|-------------------|-------------------|

| (FALCONIC-EM)     | Version 1         |

# Application Note AN10233

#### **Table of Figures**

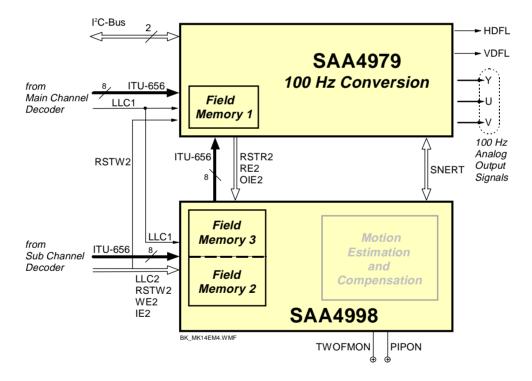

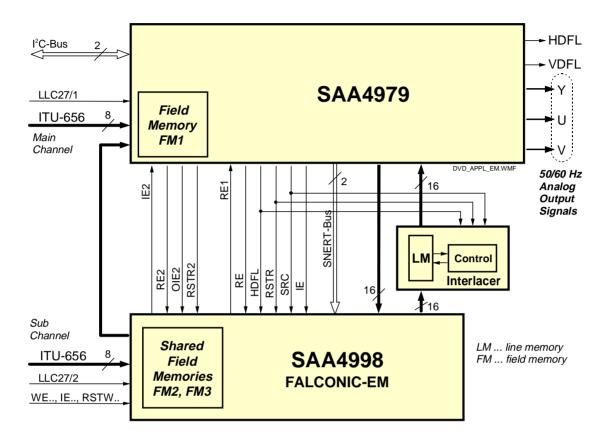

| Fig. 1             | Block diagram of the scan conversion field memory                     | <br> | <br> | <br> | <br>. 13 |

|--------------------|-----------------------------------------------------------------------|------|------|------|----------|

| Fig. 2             | Scan conversion modes A-A-B-B and A-B-A-B                             | <br> | <br> | <br> | <br>. 14 |

| Fig. 3             | Function of a median filter                                           | <br> | <br> | <br> | <br>. 14 |

| Fig. 4             | Median filter used to generate interpolated pictures                  | <br> | <br> | <br> | <br>. 15 |

| Fig. 5             | Moving bars: motion artefacts along the edges                         | <br> | <br> | <br> | <br>. 16 |

| Fig. 6             | Scan conversion with and without motion compensation                  | <br> | <br> | <br> | <br>. 17 |

| Fig. 7             | 2:2 pull-down movie move                                              | <br> | <br> | <br> | <br>. 18 |

| Fig. 8             | 3:2 pull-down movie move                                              | <br> | <br> | <br> | <br>. 18 |

| Fig. 9             | Motion compensation in 2:2 pull-down movie mode                       | <br> | <br> | <br> | <br>. 19 |

| Fig. 10            | Motion compensation in 3:2 pull-down movie mode                       | <br> | <br> | <br> | <br>. 19 |

| Fig. 11            | Interlaced display vs. progressive display                            | <br> | <br> | <br> | <br>. 20 |

| Fig. 12            | Format comparison 50 Hz / 100 Hz / 75 Hz                              |      |      |      |          |

| Fig. 13            | Motion compensation in 75i mode                                       |      |      |      |          |

| Fig. 14            | Scan conversion from 50 Hz interlace to 60 Hz progressive             |      |      |      |          |

| Fig. 15            | Motion compensation in 50i/60p conversion mode                        |      |      |      |          |

| Fig. 16            | Single clock and dual clock system in scan conversion                 |      |      |      |          |

| Fig. 18            | ITU-656 multiplex signal                                              |      |      |      |          |

| Fig. 17            | Block diagram of the SAA4979H                                         |      |      |      |          |

| Fig. 19            | ITU-656 horizontal timing                                             |      |      |      |          |

| Fig. 20            | ITU-656 timing reference codes                                        |      |      |      |          |

| Fig. 21            | ITU-656 vertical timing                                               |      |      |      |          |

| Fig. 22            | Digital levels of Y input signal for color bar 100/0/75/0 (ITU-601)   |      |      |      |          |

| Fig. 23            | Digital levels of U input signal for color bar 100/0/75/0 (ITU-601)   |      |      |      |          |

| Fig. 24            | Digital levels of V input signal for color bar 100/0/75/0 (ITU-601) . |      |      |      |          |

| Fig. 25            | Dealing with letterbox transmissions                                  |      |      |      |          |

| Fig. 25<br>Fig. 26 | Block diagram of the black bar detection                              |      |      |      |          |

| •                  |                                                                       |      |      |      |          |

| Fig. 27            | Basic block diagram of the DNR circuit                                |      |      |      |          |

| Fig. 28            | Sample noise reduction k-curve                                        |      |      |      |          |

| Fig. 29            | Defining a k-curve.                                                   |      |      |      |          |

| Fig. 30            | Block diagram of noise estimator                                      |      |      |      |          |

| Fig. 31            | Clipping levels in the SOB calculation                                |      |      |      |          |

| Fig. 32            | Calculation of the interval upper boundary upbnd                      |      |      |      |          |

| Fig. 33            | Block diagram of the scan conversion memory                           |      |      |      |          |

| Fig. 34            | Sample rate conversion by interpolation                               |      |      |      |          |

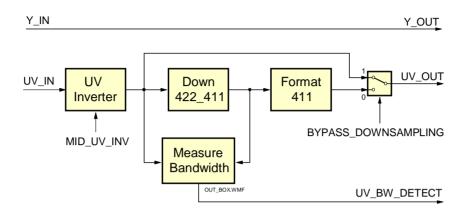

| Fig. 35            | Block diagram of the output part of the expansion port                |      |      |      |          |

| Fig. 36            | Block diagram of the input part of the expansion port                 |      |      |      |          |

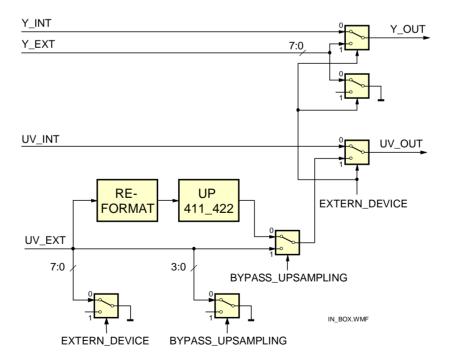

| Fig. 37            | Principle of panoramic zoom                                           |      |      |      |          |

| Fig. 38            | Nonlinear compression/expansion in panorama mode                      |      |      |      |          |

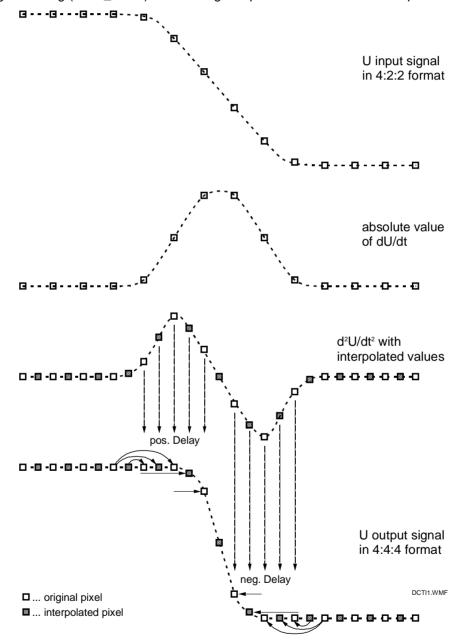

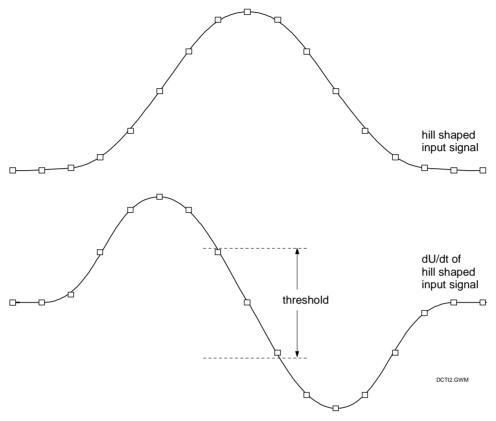

| Fig. 39            | DCTI basic operating principle                                        |      |      |      |          |

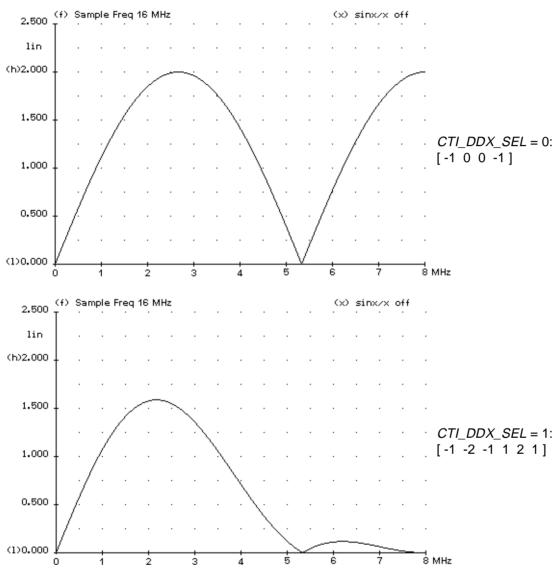

| Fig. 40            | Transfer curves of the first differentiating filter                   |      |      |      |          |

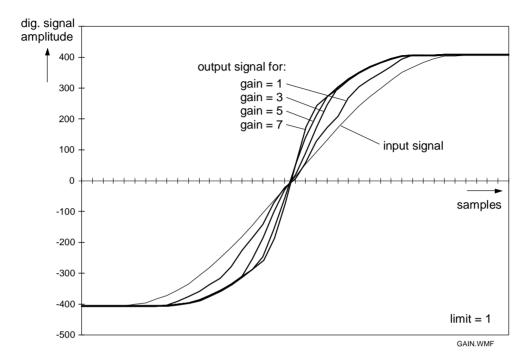

| Fig. 41            | DCTI with variation of gain for a limit setting of 1                  | <br> | <br> | <br> | <br>. 42 |

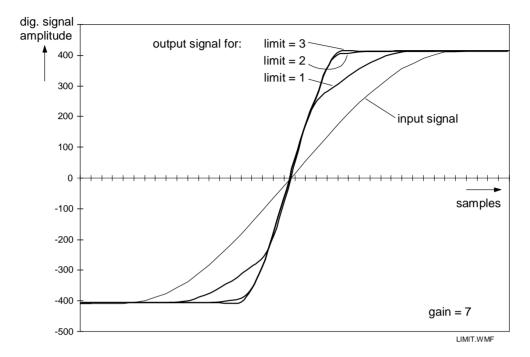

| Fig. 42            | DCTI with variation of limit for a gain setting of 7                  | <br> | <br> | <br> | <br>. 43 |

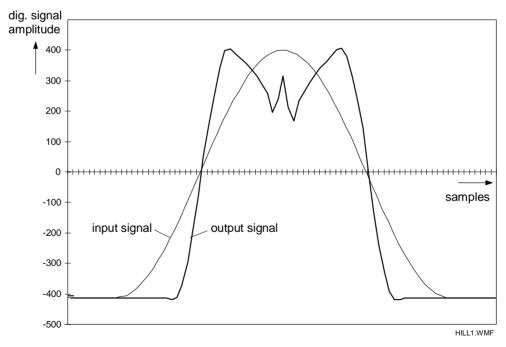

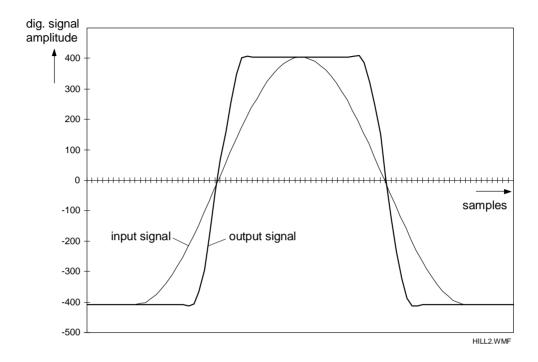

| Fig. 44            | DCTI without 'over-the-hill protection'                               | <br> | <br> | <br> | <br>. 43 |

| Fig. 43            | Principle of hill detection                                           | <br> | <br> | <br> | <br>. 44 |

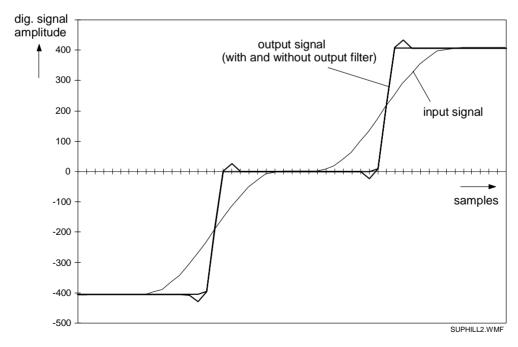

| Fig. 47            | DCTI with superhill-protection on                                     | <br> | <br> | <br> | <br>. 44 |

| Fig. 45            | DCTI with over-the-hill-protection                                    | <br> | <br> | <br> | <br>. 45 |

| Fig. 46            | DCTI with superhill-protection off                                    | <br> | <br> | <br> | <br>. 45 |

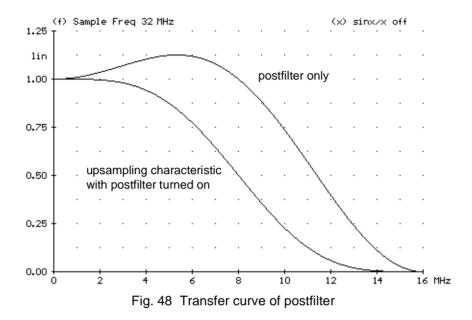

| Fig. 48            | Transfer curve of postfilter                                          | <br> | <br> | <br> | <br>. 46 |

|                    |                                                                       |      |      |      |          |

|         | conversion using the SAA4998 CONIC-EM) Version 1                                 | Application Note<br>AN10233 |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|--|

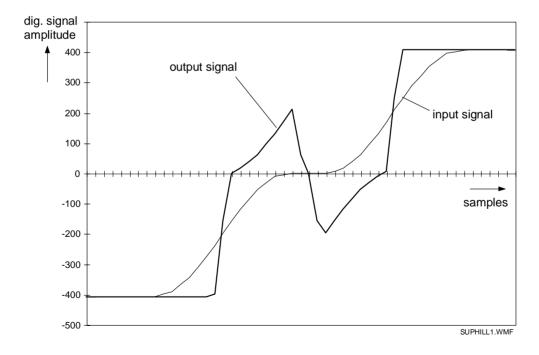

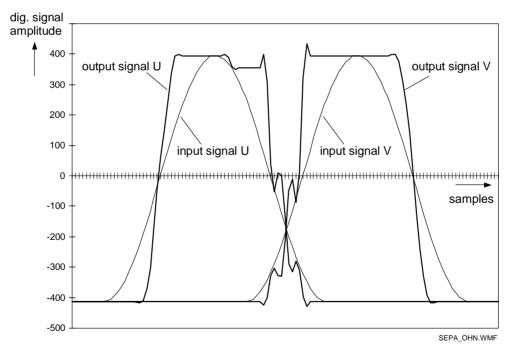

| Fig. 49 | DCTI with common processing of both signals (CTI_SEPARATE = 0)                   | 46                          |  |  |  |  |  |  |

| Fig. 50 | DCTI with separate processing of both signals (separate = 1)                     |                             |  |  |  |  |  |  |

| •       |                                                                                  |                             |  |  |  |  |  |  |

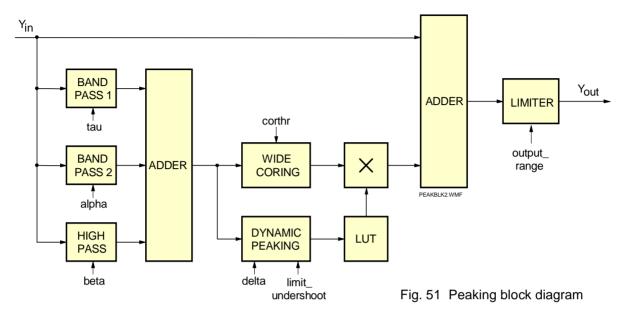

| Fig. 51 | Peaking block diagram                                                            |                             |  |  |  |  |  |  |

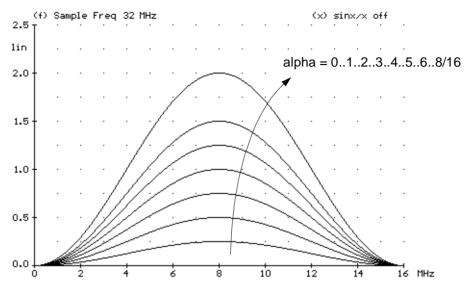

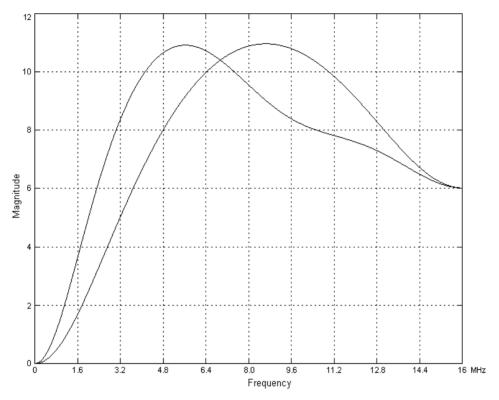

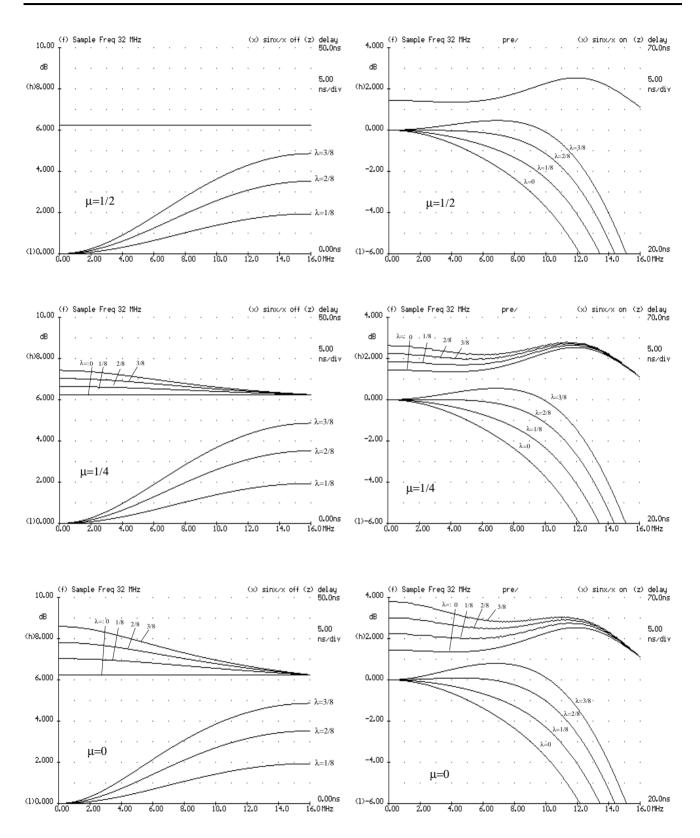

| Fig. 52 | Frequency response of the peaking band pass filter 1                             |                             |  |  |  |  |  |  |

| Fig. 53 | Frequency response of the peaking band pass filter 2                             |                             |  |  |  |  |  |  |

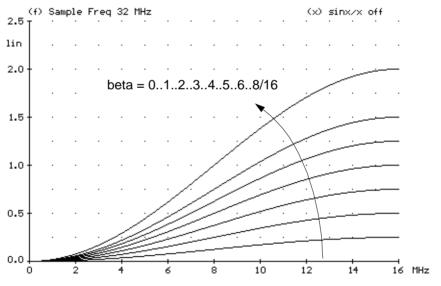

| Fig. 54 | Frequency response of the peaking high pass filter                               |                             |  |  |  |  |  |  |

| Fig. 55 | Variation of peaking center frequency                                            |                             |  |  |  |  |  |  |

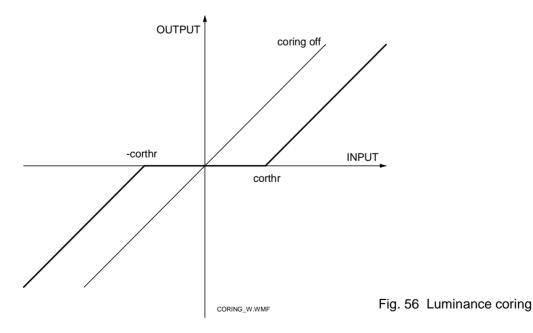

| Fig. 56 | Luminance coring                                                                 |                             |  |  |  |  |  |  |

| Fig. 57 | Dynamic peaking control                                                          |                             |  |  |  |  |  |  |

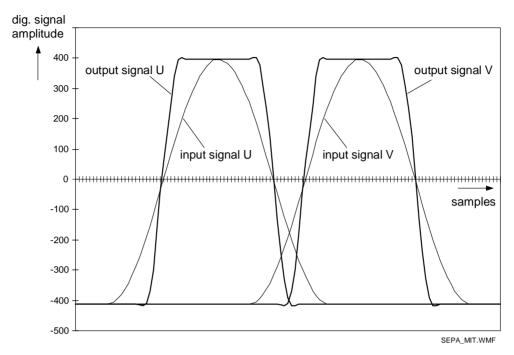

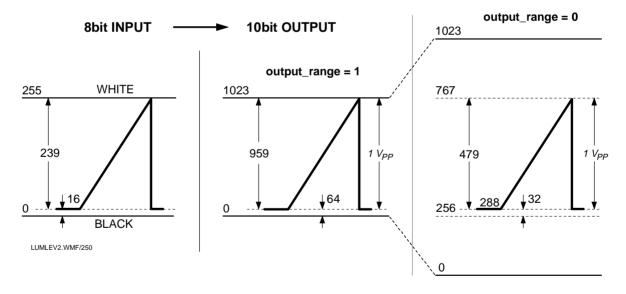

| Fig. 58 | Input / output signal levels of luminance signal                                 |                             |  |  |  |  |  |  |

| Fig. 59 | Group delay and transfer curves of the NLP D/A filter                            | 52                          |  |  |  |  |  |  |

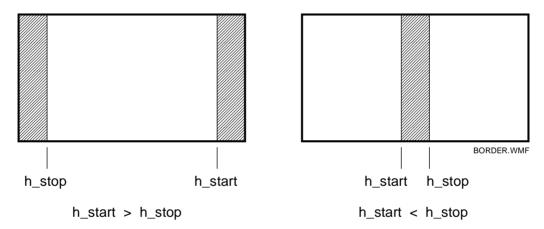

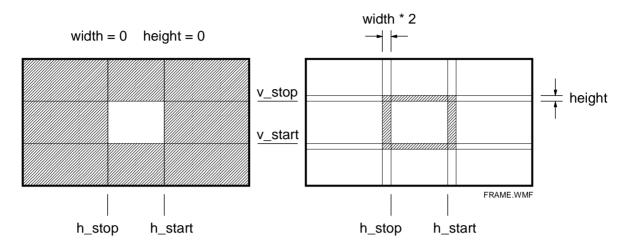

| Fig. 61 | Border definition                                                                | 53                          |  |  |  |  |  |  |

| Fig. 60 | NLP D/A gain settings                                                            | 53                          |  |  |  |  |  |  |

| Fig. 62 | Frame definition                                                                 | 54                          |  |  |  |  |  |  |

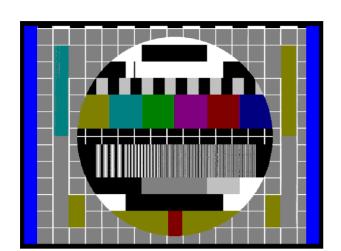

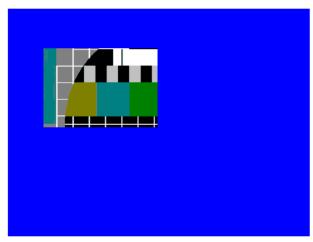

| Fig. 63 | Examples for windows and frames                                                  | 55                          |  |  |  |  |  |  |

| Fig. 64 | Luminance and chrominance output levels                                          |                             |  |  |  |  |  |  |

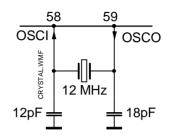

| Fig. 65 | Application diagram of Crystal for PLL                                           |                             |  |  |  |  |  |  |

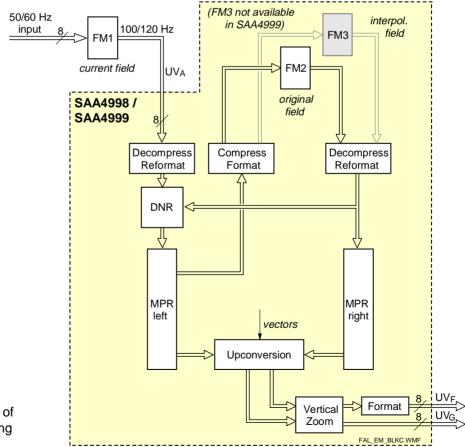

| Fig. 66 | Block diagram of the SAA4998                                                     |                             |  |  |  |  |  |  |

| Fig. 67 | 100 Hz field repetition causes blurring at moving edges                          |                             |  |  |  |  |  |  |

| Fig. 68 | Block matching principle                                                         |                             |  |  |  |  |  |  |

| Fig. 69 | Block diagram of the SAA4993 luminance processing                                |                             |  |  |  |  |  |  |

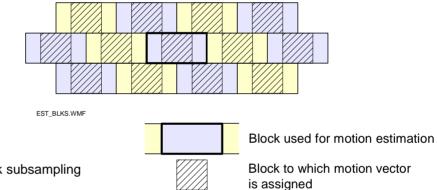

| •       | Motion estimator block subsampling                                               |                             |  |  |  |  |  |  |

| Fig. 70 |                                                                                  |                             |  |  |  |  |  |  |

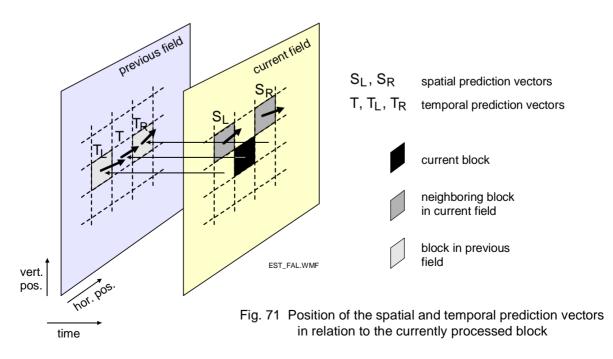

| Fig. 71 | Position of the spatial and temporal prediction vectors in relation to the curre |                             |  |  |  |  |  |  |

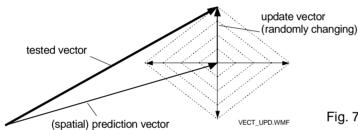

| Fig. 72 | Recursive search trying to find a better vector                                  |                             |  |  |  |  |  |  |

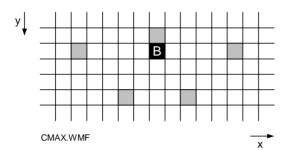

| Fig. 73 | Selection of Cmax                                                                |                             |  |  |  |  |  |  |

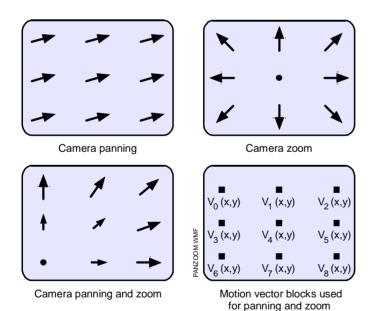

| Fig. 74 | Motion vectors for panning and zooming                                           |                             |  |  |  |  |  |  |

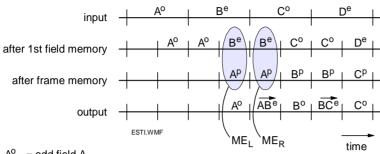

| Fig. 75 | Two estimations per input field                                                  |                             |  |  |  |  |  |  |

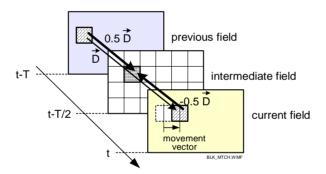

| Fig. 76 | Split vectors                                                                    |                             |  |  |  |  |  |  |

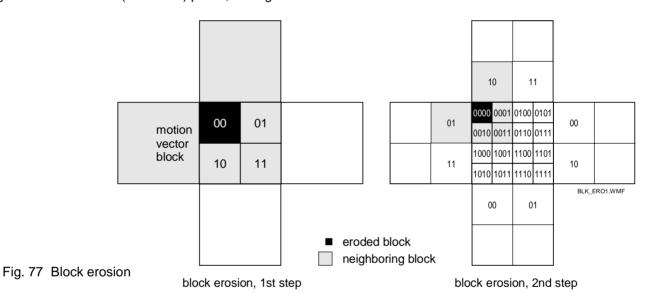

| Fig. 77 | Block erosion                                                                    | 65                          |  |  |  |  |  |  |

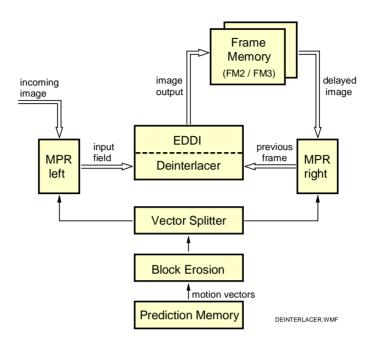

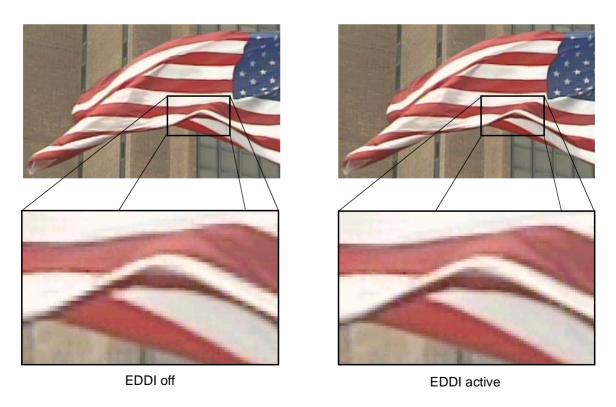

| Fig. 78 | Deinterlacing with EDDI                                                          | 66                          |  |  |  |  |  |  |

| Fig. 79 | Removing deinterlacing artefacts with EDDI                                       | 66                          |  |  |  |  |  |  |

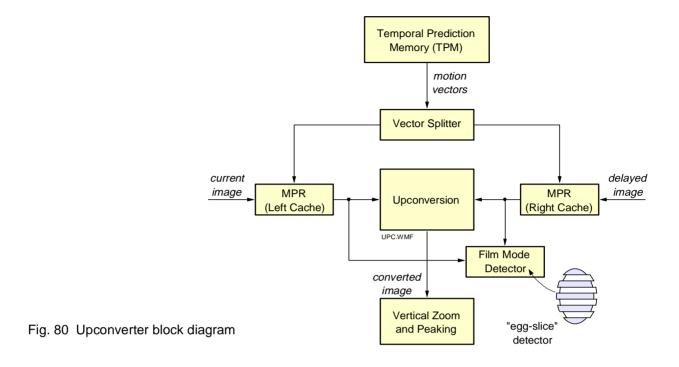

| Fig. 80 | Upconverter block diagram                                                        | 68                          |  |  |  |  |  |  |

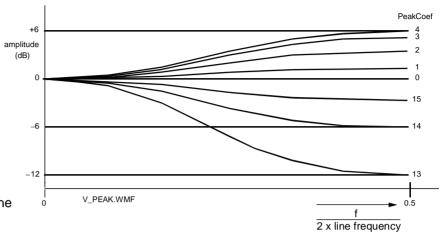

| Fig. 81 | Frequency response of the vertical peaking function                              | 69                          |  |  |  |  |  |  |

| Fig. 82 | Block diagram of chrominance processing                                          | 69                          |  |  |  |  |  |  |

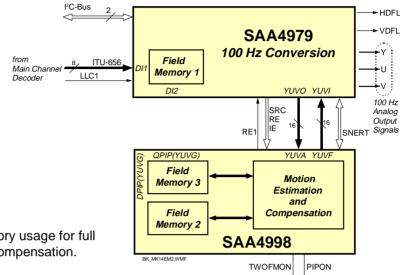

| Fig. 83 | Data flow and memory usage for full motion estimation/compensation               |                             |  |  |  |  |  |  |

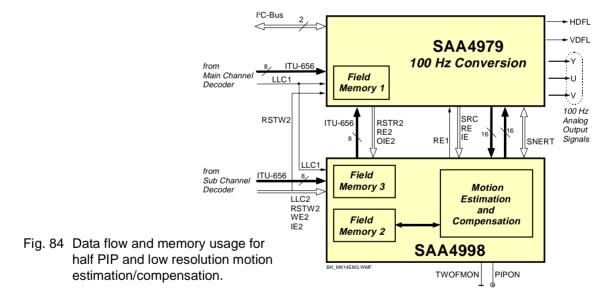

| Fig. 84 | Data flow and memory usage for half PIP and low resolution motion estimation     |                             |  |  |  |  |  |  |

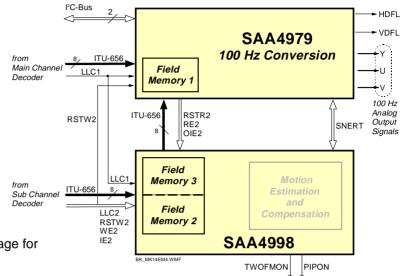

| Fig. 85 | Data flow and memory usage for highest resolution PIP                            |                             |  |  |  |  |  |  |

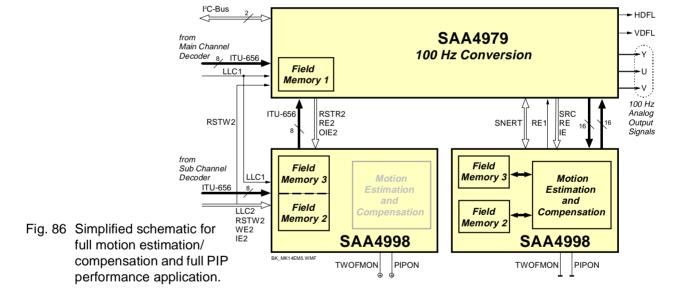

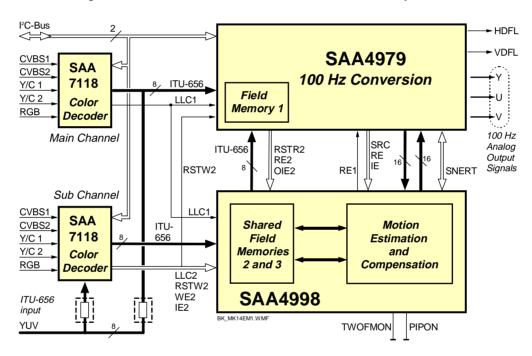

| Fig. 86 | Simplified schematic for full motion estimation/compensation and full PIP per    |                             |  |  |  |  |  |  |

| Fig. 87 | DNR block diagram                                                                | • •                         |  |  |  |  |  |  |

| Fig. 88 | Block diagram of the SAA7118                                                     |                             |  |  |  |  |  |  |

| Fig. 89 | Block diagram of the MK14-EM module                                              |                             |  |  |  |  |  |  |

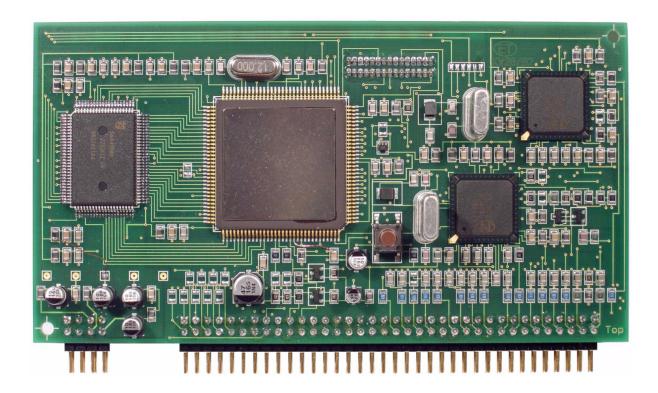

| Fig. 90 | Top view of the MK14-EM board                                                    |                             |  |  |  |  |  |  |

| •       | ·                                                                                |                             |  |  |  |  |  |  |

| Fig. 91 | Running the MK14-EM board without subchannel and motion compensation.            |                             |  |  |  |  |  |  |

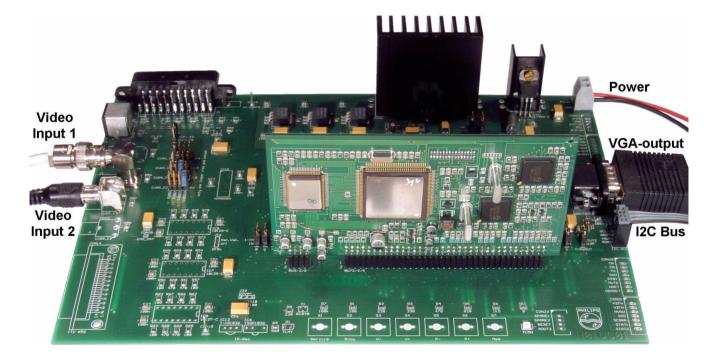

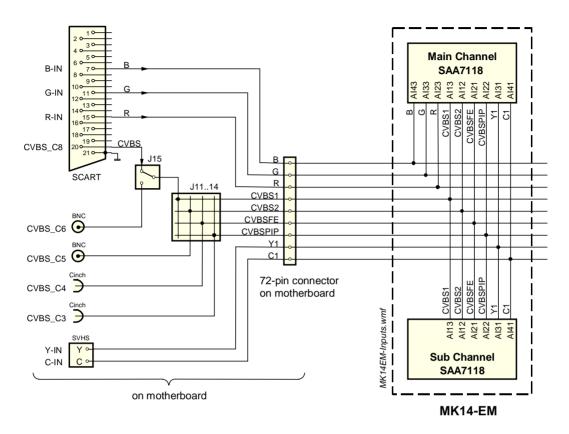

| Fig. 92 | IPQ board MK14-EM on mother board                                                |                             |  |  |  |  |  |  |

| Fig. 93 | Input selection on mother board                                                  |                             |  |  |  |  |  |  |

| Fig. 94 | Data flow in two-channel display mode                                            |                             |  |  |  |  |  |  |

| Fig. 95 | Block diagram of motion compensation in a DVD player                             |                             |  |  |  |  |  |  |

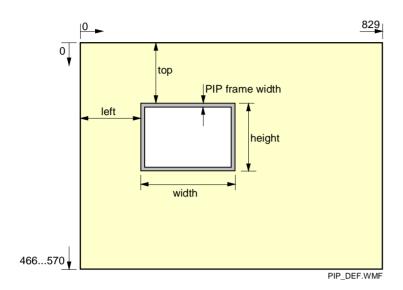

| Fig. 96 | Definition of the PIP-window                                                     |                             |  |  |  |  |  |  |

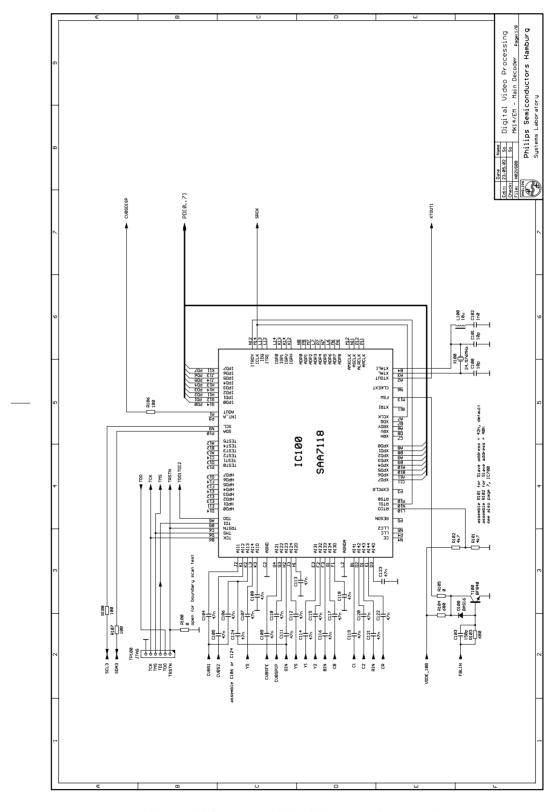

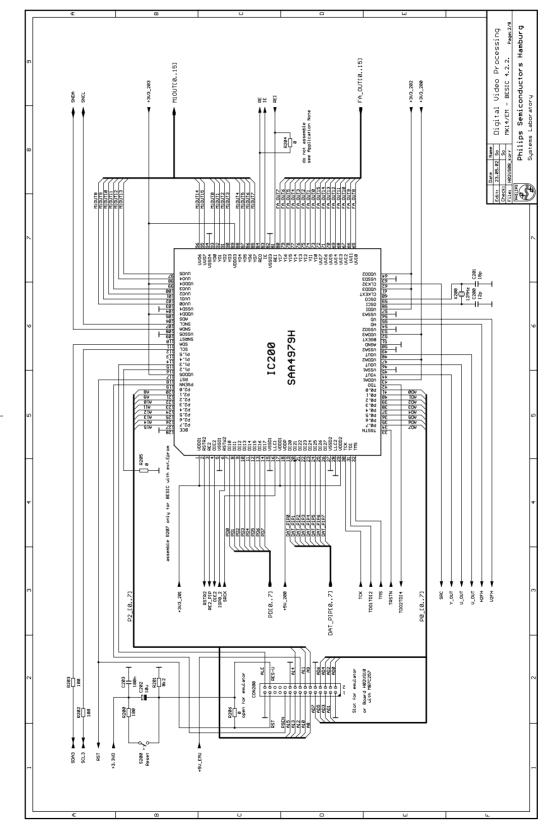

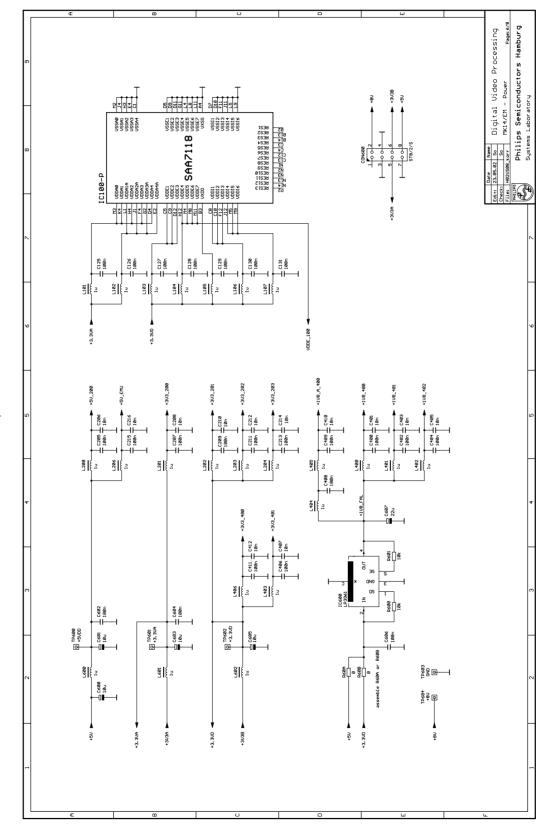

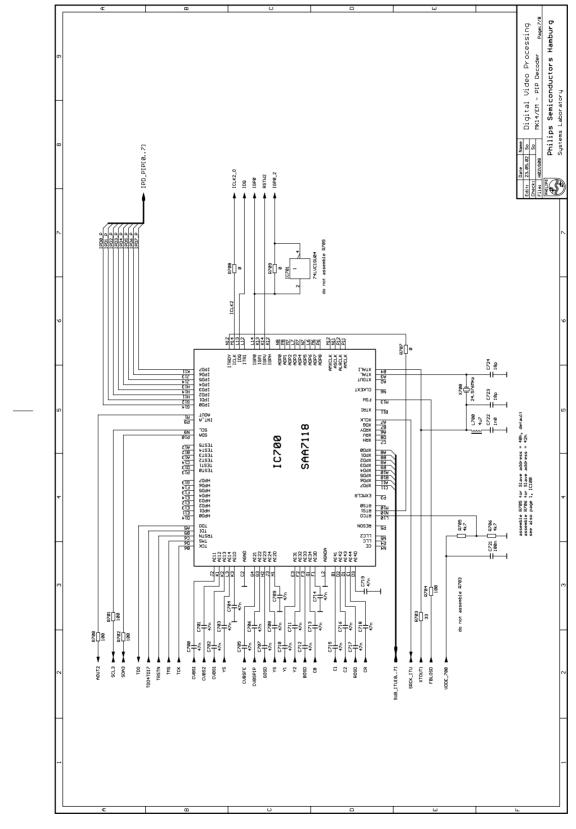

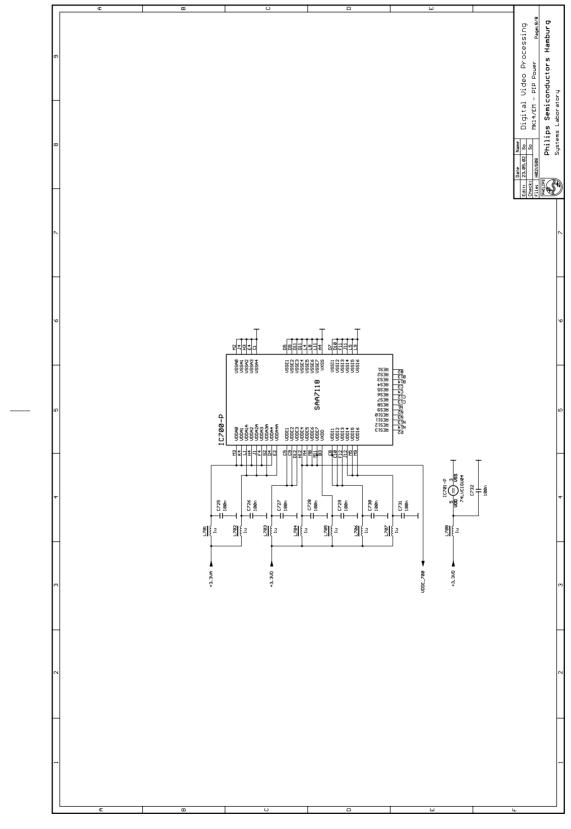

| Fig. 97 | IPQ module MK14-EM circuit diagram: sheet 1                                      |                             |  |  |  |  |  |  |

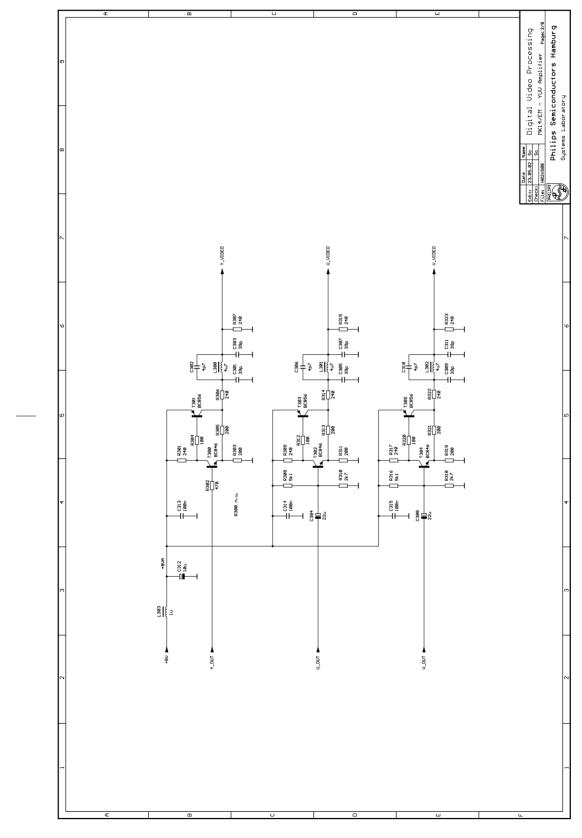

| Fig. 98 | IPQ module MK14-EM circuit diagram, sheet 2                                      | 123                         |  |  |  |  |  |  |

| Scan conversion using the (FALCONIC-EM) |                            | the SAA4998<br>Version 1 |       |  | Application Note AN1023 |      |  |  |  |  |  |      |     |

|-----------------------------------------|----------------------------|--------------------------|-------|--|-------------------------|------|--|--|--|--|--|------|-----|

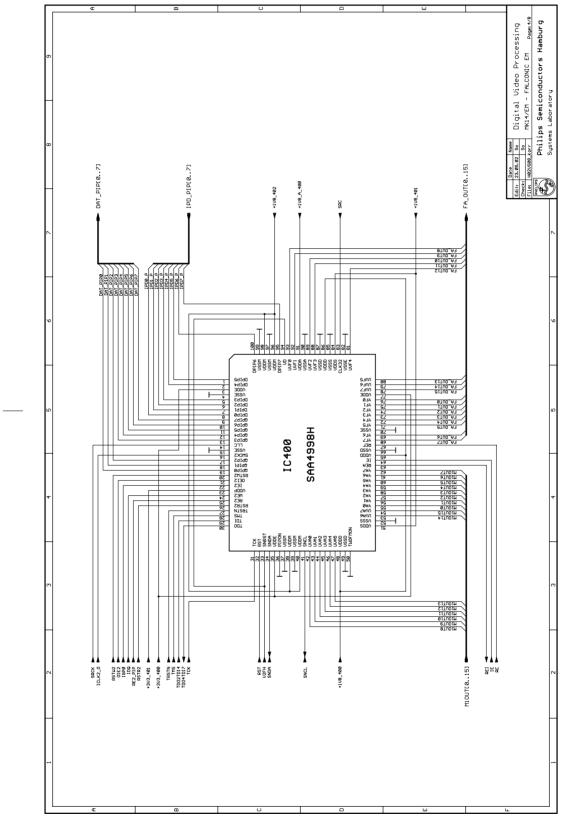

| Fig. 99                                 | IPQ module MK14-EM circui  | t diagram: sheet 3.      |       |  | <br>                    | <br> |  |  |  |  |  | <br> | 124 |

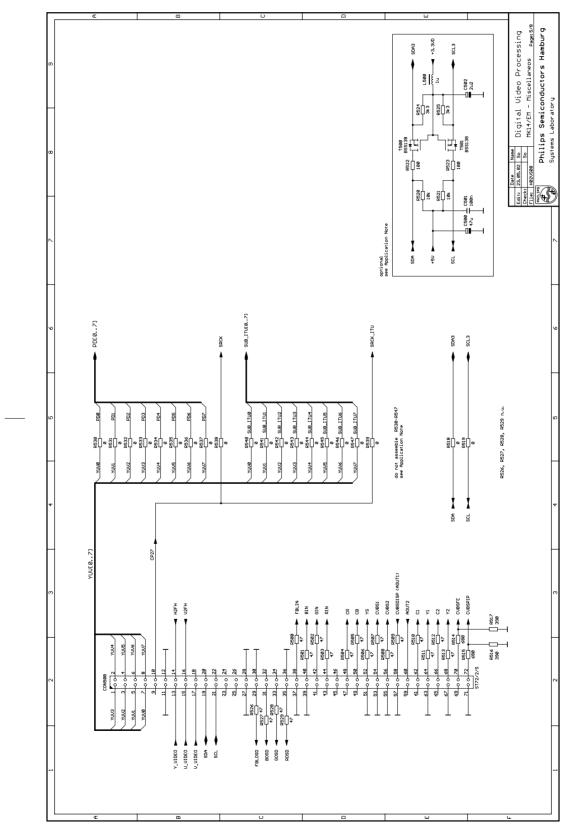

| Fig. 100                                | IPQ module MK14-EM circuit | t diagram: sheet 4.      |       |  | <br>                    | <br> |  |  |  |  |  | <br> | 125 |

| Fig. 101                                | IPQ module MK14-EM circuit | t diagram: sheet 5.      |       |  | <br>                    | <br> |  |  |  |  |  | <br> | 126 |

| Fig. 102                                | IPQ module MK14-EM circuit | t diagram: sheet 6.      |       |  | <br>                    | <br> |  |  |  |  |  | <br> | 127 |

| Fig. 103                                | IPQ module MK14-EM circuit | t diagram: sheet 7.      |       |  | <br>                    | <br> |  |  |  |  |  | <br> | 128 |

| Fig. 104                                | IPQ module MK14-EM circuit | t diagram: sheet 8.      |       |  | <br>                    | <br> |  |  |  |  |  | <br> | 129 |

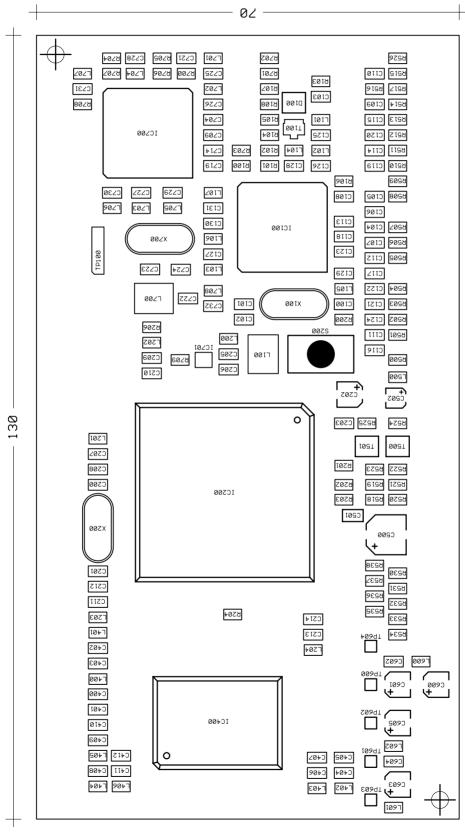

| Fig. 105                                | IPQ module MK14-EM: posit  | ion of part (top side    | e)    |  | <br>                    | <br> |  |  |  |  |  | <br> | 130 |

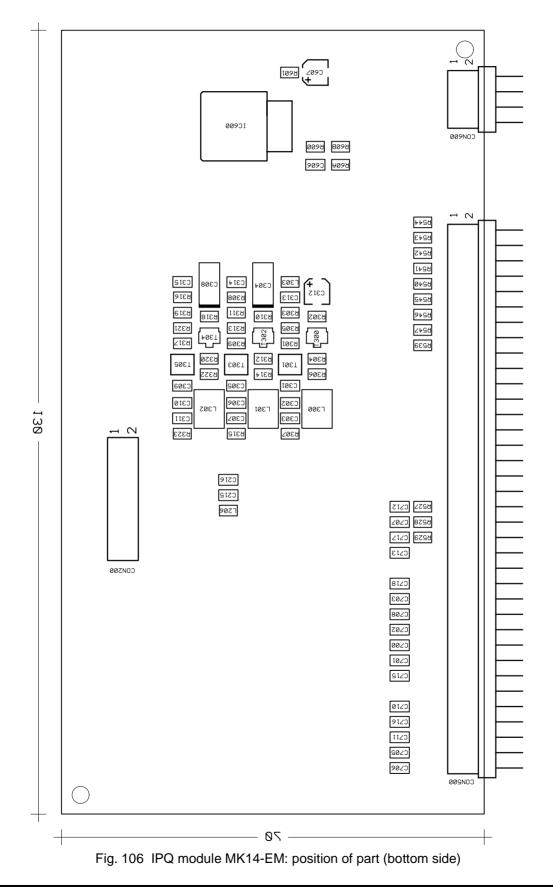

| Fig. 106                                | IPQ module MK14-EM: posit  | ion of part (bottom      | side) |  | <br>                    | <br> |  |  |  |  |  | <br> | 131 |

Application Note AN10233

#### 1. Introduction

The MK14-EM module is a scan converter for television input signals. The converter doubles the line frequency, the output field frequency depends on the mode. It can also be doubled, in this case 50 Hz PAL/SECAM or 60 Hz NTSC are changed to 100 Hz or 120 Hz. Or it can remain unchanged as is the case in progressive scan conversion (deinterlacing).

The module offers various analog input, but also can be configured to accept digital video data in ITU-656 format. The output signals are analog YUV. There are two color decoders on board enabling two video sources to be displayed at the same time, either in double window or PIP (picture-in-picture) mode.

The scan conversion IC on the board is the SAA4979. It decodes the digital video input streams, has a built-in scan conversion memory, offers various picture improvement functions and has D/A converters to generate the analog output signals. On-chip the SAA4979 also has a microcontroller with embedded RAM and ROM and an I<sup>2</sup>C interface for communication with a main controller.

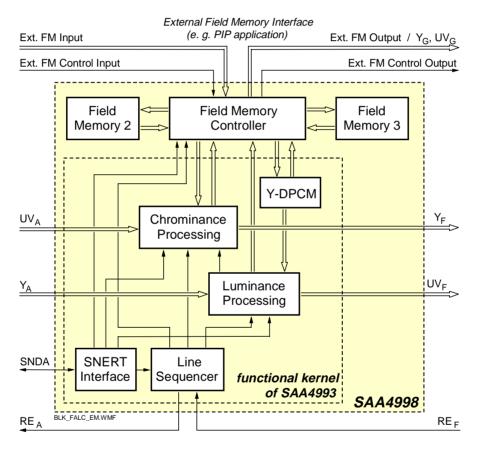

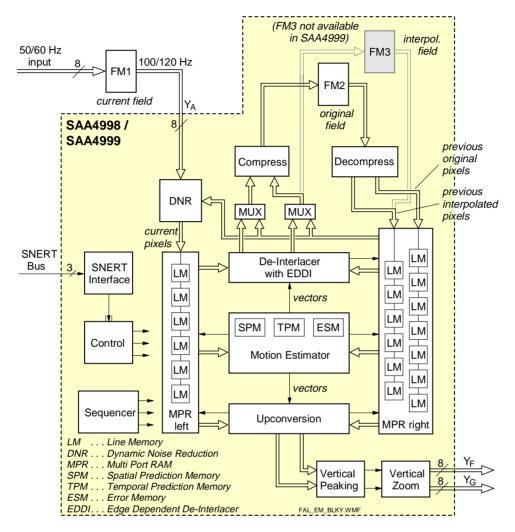

Motion compensation on the converted signal is done by the SAA4998 (FALCONIC-EM). This IC has the core functions of the SAA4993 (FALCONIC), but also has two field memories on-chip (EM stands for 'embedded memories') which are needed for motion compensation. These memories can also be configured differently, in that case one or both of them serve as buffer memory for video data in the subchannel (PIP memory).

This application note describes the hardware functions of the SAA4979 and SAA4998 and the application environment needed to realize 100 Hz scan conversion as well as extra functions. A register command table is added (chapter 10), this is the control interface to an outside master controller or to a user who wants to define certain settings of the board.

# Application Note AN10233

#### 2. Features of IPQ modules

Table 1 gives an overview of the MK14-EM scan converter modules. The individual modules are equipped with a SAA4998 or SAA4999 and one or two color decoders SAA7118.

Module 1: MK14-EM equipped with SAA4998 and 2 x SAA7118

Module 2: MK14-EM equipped with SAA4999 and 2 x SAA7118

Module 3: MK14-EM equipped with SAA4999 and SAA7118

| module:                                                                                                             | 1                          | 2                          | 3                                      |

|---------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------------------|

| Feature                                                                                                             | MK14-EM<br>with<br>SAA4998 | MK14-EM<br>with<br>SAA4999 | MK14-EM<br>with<br>SAA4999<br>(no PIP) |

| 4:2:2 scan rate doubling (50 to 100 Hz or 60 to 120 Hz)                                                             | х                          | х                          | х                                      |

| 4:2:2 conversion to progressive scan (50 Hz / 60 Hz proscan)                                                        |                            |                            |                                        |

| 4:2:2 conversion 50 Hz to 75 Hz or 60 Hz to 90 Hz                                                                   |                            |                            |                                        |

| 4:2:2 conversion 50 Hz interlace to 60 Hz progressive                                                               |                            |                            |                                        |

| 3.5 MBit embedded scan conversion memory                                                                            | х                          | х                          | х                                      |

| Embedded memories for motion compensation / PIP                                                                     | 2                          | 1                          |                                        |

| Sample rate conversion for linear zoom and compression                                                              | х                          | х                          | х                                      |

| Panorama mode                                                                                                       | х                          | х                          | х                                      |

| Dynamic noise reduction                                                                                             | х                          | х                          | х                                      |

| Noise estimator                                                                                                     | х                          | х                          | х                                      |

| Black bar detection                                                                                                 | х                          | х                          | х                                      |

| Luminance horizontal smart peaking                                                                                  | х                          | х                          | х                                      |

| Digital Color Transient Improvement (DCTI)                                                                          | х                          | Х                          | х                                      |

| Triple 10-bit Digital-to-Analog Converter (DAC)                                                                     | х                          | х                          | х                                      |

| Line locked PLL                                                                                                     | х                          | х                          | х                                      |

| Double window and picture-in-picture processing                                                                     | х                          | х                          |                                        |

| Embedded 80C51 microprocessor with 32 kB ROM and 512 Bytes RAM                                                      | х                          | х                          | х                                      |

| I <sup>2</sup> C-bus controlled                                                                                     | х                          | х                          | х                                      |

| Motion compensated upconversion of 1 f <sub>H</sub> video and film standards up to 292 active input lines per field | Х                          | х                          |                                        |

| Motion compensated upconversion of 50 Hz <b>video</b> or <b>film</b> standard (2:1) to 100 Hz (2:1)                 | х                          | x <sup>1</sup>             |                                        |

Table 1: Features of IPQ modules

# Application Note AN10233

| module:                                                                                         | 1                          | 2                          | 3                                      |

|-------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------------------|

| Feature                                                                                         | MK14-EM<br>with<br>SAA4998 | MK14-EM<br>with<br>SAA4999 | MK14-EM<br>with<br>SAA4999<br>(no PIP) |

| Motion compensated upconversion of 50 Hz <b>video</b> standard (2:1) to 50 Hz progressive (1:1) | х                          | х                          |                                        |

| Motion compensated upconversion of 50 Hz <b>film</b> standard (2:1) to 50 Hz progressive (1:1)  | х                          |                            |                                        |

| Motion compensated upconversion of 60 Hz <b>video</b> standard (2:1) to 60 Hz progressive (1:1) | х                          | х                          |                                        |

| Motion compensated upconversion of 60 Hz <b>film</b> standard (2:1) to 60 Hz progressive (1:1)  | х                          |                            |                                        |

| 3:2 pull-down motion compensation of 60 Hz film standard                                        | х                          |                            |                                        |

| Full 8-bit accuracy                                                                             | Х                          | Х                          | х                                      |

| Edge dependent de-interlacing (EDDI)                                                            | Х                          | Х                          |                                        |

| Variable vertical sharpness enhancement                                                         | Х                          | Х                          |                                        |

| Motion compensated 3D dynamic noise reduction                                                   | Х                          | Х                          |                                        |

| High quality vertical zoom                                                                      | Х                          | Х                          |                                        |

| On-board color decoder for main picture                                                         | Х                          | Х                          | х                                      |

| On-board color decoder for subchannel (double window or PIP=picture-in-picture)                 | х                          | х                          |                                        |

Table 1: Features of IPQ modules

1. Reduced performance in film mode

#### 3. Scan conversion overview

In this chapter an overview is given on the reasons for scan conversion as well as the various scan conversion modes offered by the Philips IPQ board. The modes can be divided into three main groups:

- scan rate doubling (50 Hz to 100 Hz or 60 Hz to 120 Hz)

- conversion to progressive scan (50 / 60 Hz interlace to 50 / 60 Hz progressive)

- non-integer scan rate conversion (50 Hz to 75 Hz, 60 Hz to 90 Hz, 50 Hz to 60 Hz)

#### 3.1 Reasons for scan conversion

In standard TV systems (PAL, NTSC, SECAM) pictures are transmitted sequentially. The frequency is either 50 Hz (PAL, SECAM) or 60 Hz (NTSC). Originally it was defined according to the power line frequency of the respective countries in order to avoid interference. Both frequencies are so low that flickering is noticeable, with 50 Hz being clearly visible in large bright areas, while 60 Hz is not really annoying any more. "Flicker free" starts from 70 Hz on upwards.

For 50 Hz systems an increase in scan rate is therefore an essential picture improvement. Doubling the scan rate is technically the simplest approach and was therefore favored for many years. Now different conversion ratios like 50 to 75 Hz are also implemented.

The 60 Hz NTSC system has fewer lines than the 50 Hz systems (525 instead of 625), therefore line visibility, line flickering and less vertical resolution are more annoying than large area flickering. All these points can be effectively improved by conversion to progressive scan (non-interlace mode). This doubles the number of lines per field but leaves the field frequency unchanged.

#### 3.2 Scan rate doubling

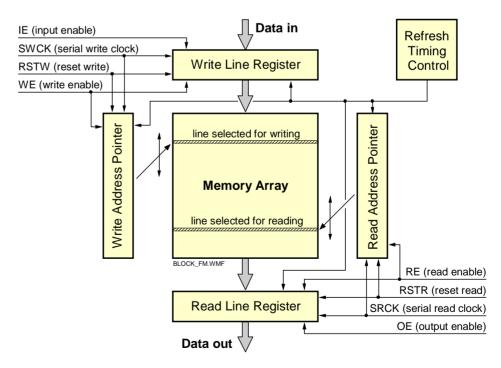

In scan rate doubling each input field in written into a memory and read from the memory at double the input clock and double line and field frequency. Advantageous are memories which allow writing and reading at the same time. On the other hand, random access is generally not required, the operation is more like a FIFO (first in - first out). Therefore these video memories do not need external addressing, address counters are internal. Just a reset is required on the input and output side to define the start of the field being written or read. Fig. 1 shows the block diagram of such a field memory.

Fig. 1 Block diagram of the scan conversion field memory

### Application Note AN10233

#### 3.3 Field repetition and frame repetition

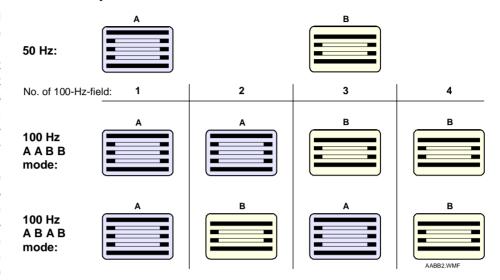

TV pictures are transmitted in interlace format, each two fields make up one frame. The field frequency is 50 Hz (PAL, SECAM) or 60 Hz (NTSC), the frame rate thus 25 Hz or 30 Hz resp. In scan rate doubling two approaches are possible: field doubling or frame doubling. When designating the two fields as field A and field B then we can talk about the modes A-A-B-B (field repetition) and A-B-A-B (frame repetition). Fig. 2 shows the two modes for a simplified 9 line TV picture.

In A-A-B-B mode interlace line flickering of 25 Hz (30

Fig. 2 Scan conversion modes A-A-B-B and A-B-A-B

Hz) is still present, whereas in A-B-A-B mode it is practically not noticeable any more. With large area flickering being gone, the remaining 25 Hz line flickering in A-A-B-B mode is even more visible and annoying, therefore conversion to A-B-A-B mode is favorable because the line flicker frequency is doubled to 50 Hz.

#### 3.4 Video mode and movie mode

In video mode (pictures taken by an electronic camera) every field represents another movement phase, so the rate is 50 (or 60 in NTSC) movements per second. We talk about movie mode (or film mode) if two consecutive fields are scanned from the same movie picture (running at 25 frames per second). In this case there is no movement between these two fields, the rate of movement phases is 25 per second.

If a movie is transmitted it is advantageous to choose A-B-A-B mode to reduce line flickering. In video mode however this sequence displays two movement phases in one frame generating contours and unsharpness around moving objects, therefore A-A-B-B mode is more suitable here.

#### 3.5 Line flicker reduction (LFR)

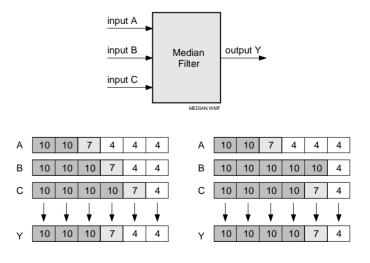

In order to eliminate the line flickering for video sources and display these pictures in A-B-A-B mode also, a median filter is used. This filter has three inputs (pixel values) and outputs the median one, i. e. it discards the extreme values of the three. Fig. 3 show the basic principle.

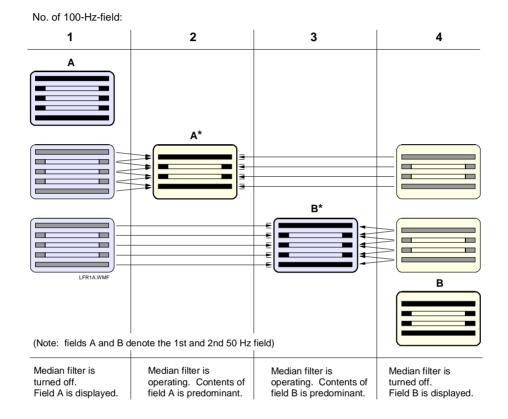

This filter is used to generate the interpolated pictures in 100 Hz mode, see fig. 4. 100 Hz fields no. 1 and 4 are the original 50 Hz fields A and B, here the median filter is turned off. 100 Hz fields no. 2 and 3 have the median filter activated. In field 2 two of the filter inputs carry information from the neighboring lines of field A, one input has line information from field B. So picture content from field A dominates. This field is called

Fig. 3 Function of a median filter

A\*. In 100 Hz field no. 3 two filter inputs have field B information and one has field A information, so the content of field B dominates. Whenever the line information from the non-dominating field fits in between the lines of the dominating field, this line is output. In all other cases the median value is that of the dominating field. These decisions are taken on a pixel-by-pixel basis, so the filter can be seen as switch between an A-A-B-B and A-B-A-B display on a pixel-by-pixel basis, depending on the picture content.

Fig. 4 Median filter used to generate interpolated pictures

The above described line flicker reduction mode is also known as *Digital Scan* in Philips IPQ concepts.

#### 3.6 Display of moving objects

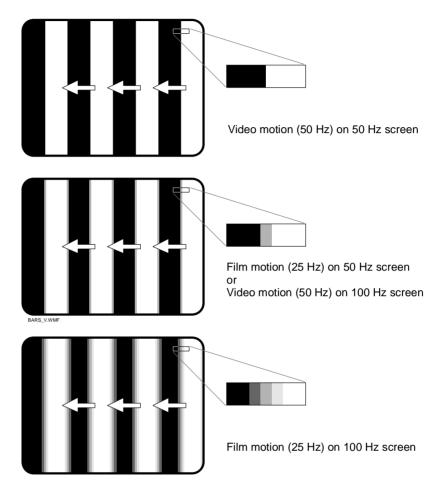

When a movie (25 movements per second) is viewed on a 50 Hz TV screen, moving objects do not move smoothly but show a judder or double contour. This is due to the fact that the rate of movement (25 Hz) is not equal to the display rate (50 Hz), see fig. 5 center. A similar effect occurs when the display rate is increased to 100 Hz. With scenes transmitted in video mode (50 Hz) contours of moving objects appear double. When a movie (25 Hz) is displayed on a 100 Hz screen contours appear even four times, see fig. 5 bottom.

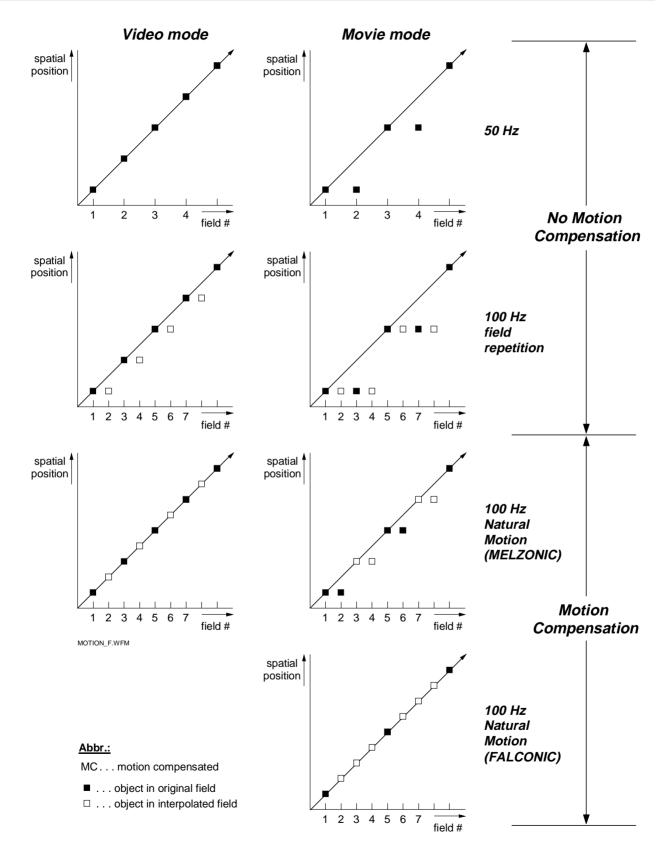

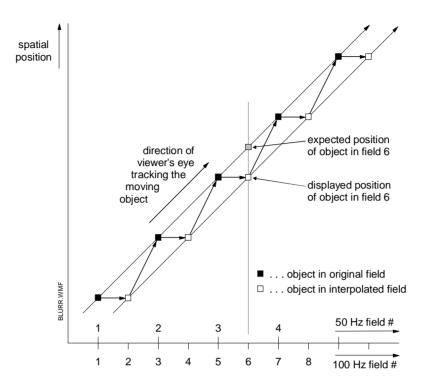

In a diagram depicting the motion of objects over time (fig. 6) the reasons for the double or multiple contours become more clear: When fields are simply repeated each object appears twice (or four times) at the same location, then jumps to next location. A viewer's eye tracing the object moves uniformly along the track and notices the off-track repetitions as contours.

In fig. 6 the upper two diagrams show video and movie sources on a 50 Hz display, here the video source will appear sharp, the movie source will be juddering due to the low-frequent (25 Hz) field repetition. The next two diagrams show the same two sources

Fig. 5 Moving bars: motion artefacts along the edges

converted to 100 Hz, here the video material will show a double contour and the movie material a fourfold contour. In the lower three diagrams motion compensation is applied to the upconverted signal. The third row depicts what was possible with Philips' first generation motion compensation IC, the SAA4991 (MELZONIC). Objects in the interpolated picture are placed in the middle between the two original positions of the actual and previous field. For movie sources this means that a remaining judder or contour is still there, because the motion rate is converted from 25 Hz to only 50 Hz, while the display rate is 100 Hz. The successor ICs SAA4992/3/4 (FALCONIC+, RAVEN) do better in this respect, they are able to convert movement from 25 Hz to 100 Hz and thus correctly position objects even in movie mode.

#### 3.7 2:2 and 3:2 pull-down movie modes

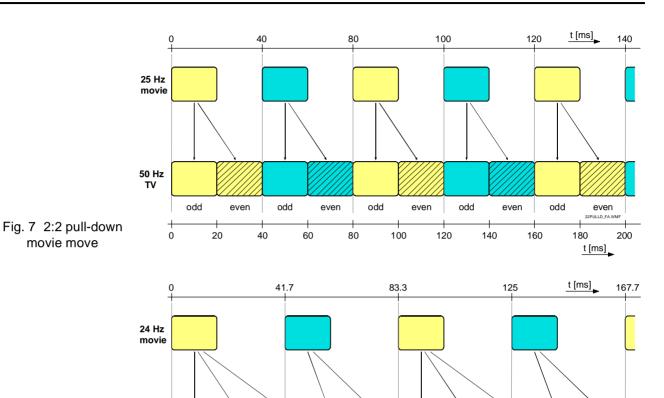

Movies are recorded on film at 24 frames per second (fps). For transmission in a PAL or SECAM TV system (50 Hz) the frame rate is increased slightly to 25 fps, and each frame is scanned twice to generate the two interlaced fields for TV. This mode is called 2:2 pull-down, see fig. 7.

For transmission in the NTSC TV system (60 Hz) a film is run at its original 24 fps. Then one frame is scanned twice and the next one three times, this gives five fields for every two film frames and a field frequency of 60 Hz. This mode is called 3:2 pull-down, see fig. 8.

Fig. 6 Scan conversion with and without motion compensation

#### **Application Note** AN10233

odd

odd

100

even

116.7

even

83.3

odd

133.3

even

t [ms]

167.7

Fig. 8 3:2 pull-down movie move

movie move

#### 3.8 Motion compensation in movie mode

60 Hz

odd

Motion estimation and compensation in movie mode is in certain ways different from video mode:

33.3

odd

even

16.7

The rate of movement is lower. Due to the frame rate of 24 or 25 frames per second the motion displacement between movement phases is about twice as large as it is in video mode with 50 or 60 movements per second. This means that the movement vector for a comparable motion is also about twice as large. After scene changes it is therefore more difficult for the estimation algorithm to set up the new vector field, and it takes somewhat longer due to the lower movement update rate.

even

66.7

50

- The proper movement phase must be determined. In the incoming video from a movie source any two consecutive fields which are taken from the same piece of film do not contain motion. Motion can only be detected between every other pair of fields which are from different film frames. It is important to determine the correct phase and combine the right two fields, because a wrong phase will deteriorate the motion rendition in the display.

- In 3:2 pull-down mode phase detection in movie mode is still more difficult. There are alternately 3 and then 2 consecutive fields without motion, and this phase has to be detected reliably.

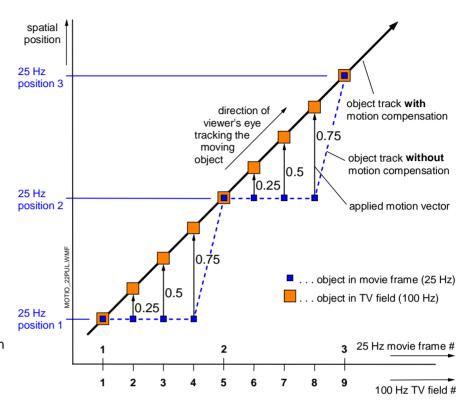

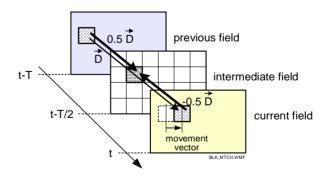

- During motion compensation the vectors found during estimation are split into different fractions. Scan rate doubling In video mode means that the interpolated field lies in-between the two original ones, so 50% of the displacement vector has to be applied for the new field. In movie mode there is only one original field and 3 interpolated ones, with an applied motion vector of 25%, 50% and 75% respectively, see fig. 9. When applying motion compensation while converting NTSC 3:2 pull-down movie to 60 Hz progressive scan, the applied motion vectors are 40%, 80%, 20% and 60% respectively, see fig. 10.

Fig. 9 Motion compensation in 2:2 pull-down movie mode

Fig. 10 Motion compensation in 3:2 pull-down movie mode

#### 3.9 Progressive scan

Especially in the NTSC standard (60 Hz), where flicker reduction is not a main feature, picture improvement by doubling the line number is preferred. This mode is called *progressive scan (proscan)* or *non-interlace*. In the 50 Hz standard this mode is possible also. The improvements are:

- Line flickering is gone. Line flickering appears along horizontal structures (transients in vertical direction) which tend to flicker with the interlace frequency of 25 Hz. This low frequency is clearly perceptible and therefore annoying.

- Line structure is gone. No more single lines are visible even from close viewing distance from the screen. The picture appears clear and smooth.

- Line crawling is gone. This effect can happen at very close viewing distance from the screen when the viewer sees the line structure moving up or down with a fixed speed, especially in areas without much detail. This effect is generated by the interlaced display. The crawling speed is 11..12 sec. per screen height in PAL and 8 sec. per screen height in NTSC.

Fig. 11 shows how two interlaced fields are combined and displayed in non-interlace (progressive) mode. If the input video is from a film source (no motion between two fields of a frame) then a field merge is done. In all other cases the median filter is active selecting the fields on a pixel-by-pixel basis

Just like in 100 Hz, in progressive scan mode the line frequency is double the input line frequency. So compared to

Field A

Field B

PROSCAN.WMF

interlaced display

progressive display

Fig. 11 Interlaced display vs. progressive display

100 Hz which is generally displayed in interlace, only the field frequency is different. TV display units can fairly easily adapt to 50 (60) Hz or 100 Hz, therefore it is possible to display PAL in 100 Hz interlace and switch to 60 Hz progressive for NTSC program sources.

#### 3.10 75 Hz interlace

As said in the beginning of this chapter, field scan rates above 70 Hz are considered "flicker free". So scan rate doubling to 100 or 120 Hz is beyond of what is necessary to eliminate flickering. But a conversion factor of 2 was easy to realize when scan conversion first came up.

Doubling the field scan rate requires to also double the horizontal scan rate and to double the analog bandwidth of the amplifier stages of the video signal when it is to be displayed on the screen with the same sharpness compared to 50 or 60 Hz. But now that these problems are solved different use can be made of these developments: with practically no change to the deflection and amplifier stages the number of visible lines (and thus pixels) can be increased by reducing the scan rate from 100 Hz to 75 Hz, a rate which also is sufficient to have a flicker free picture. The number of lines can be increased from 625 to 833 while staying with the same horizontal deflection frequency. This mode is called "75i" and is implemented in the latest version of the SAA4979's firmware. Its advantages are:

- · considerably less line visibility and line flickering

- increased vertical sharpness, if appropriate vertical peaking and signal processing is applied

- no changes in hardware, the mode runs with all 100 Hz deflection units

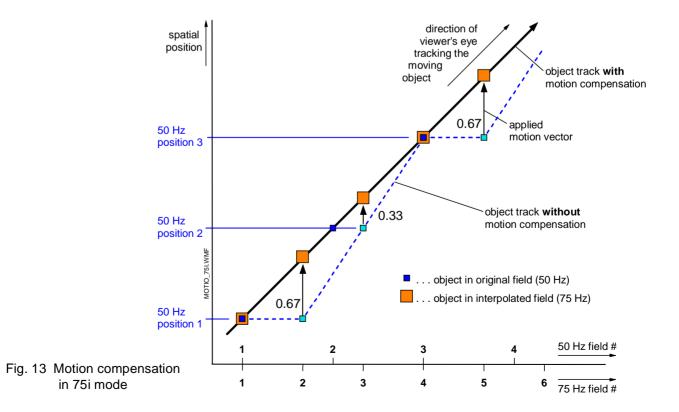

Motion compensation is also available and ensures smooth movements in video and movie mode comparable to those in 100 Hz.

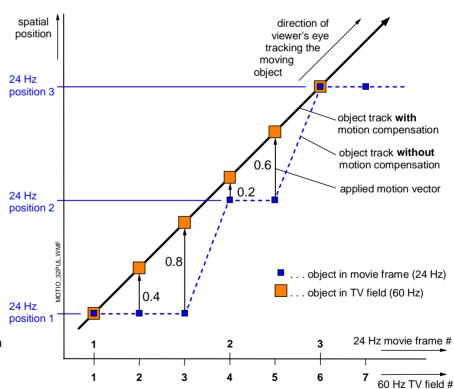

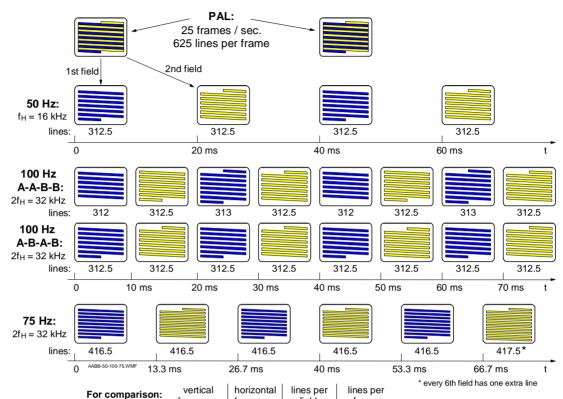

Fig. 12 shows a comparison of the scan modes 50 Hz, 100 Hz and 75 Hz. In 75 Hz every 6th field has one extra line to make the conversion come out even:

# Application Note AN10233

Fig. 12 Format comparison 50 Hz / 100 Hz / 75 Hz

| vertical  | vertical   horizontal |       | lines per |  |  |  |  |

|-----------|-----------------------|-------|-----------|--|--|--|--|

| frequency | frequency             | field | frame     |  |  |  |  |

| 50 Hz     | 16 kHz                | 312.5 | 625       |  |  |  |  |

| 100 Hz    | 32 kHz                | 312.5 | 625       |  |  |  |  |

| 75 Hz     | 32 kHz                | 416.5 | 833       |  |  |  |  |

# Application Note AN10233

100 Hz: 8 fields x 312.5 lines = 2500 lines 75 Hz: 6 fields x 416.5 lines + 1 line = 2500 lines

In order to get a stable picture in vertical scan direction, the display needs a DC-coupled deflection unit. But this is required for 100 Hz too, if the display runs in field-doubling mode (AABB) where fields are of unequal length also (312 - 312.5 - 313 - 312.5 lines)

#### 3.11 Conversion from 50 Hz to 60 Hz

In order to support applications requiring 60 Hz vertical frequency at the output, a conversion from 50 Hz to 60 Hz has been incorporated into the software. 60 Hz is not quite flickerfree, but much better than 50 Hz in that respect. Especially when it comes to driving flat panel displays 60 Hz can be favorable.

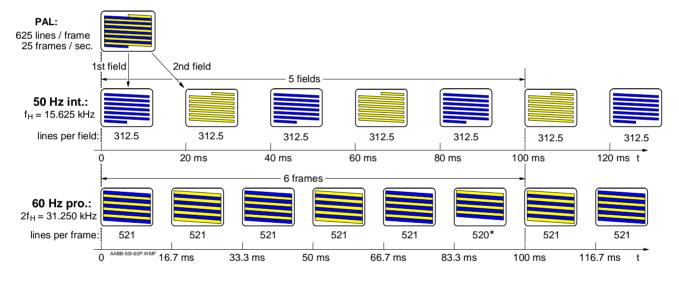

Conversion is done from 50 Hz interlace to 60 Hz progressive. This output format also runs on double the input line frequency ( $2f_H$  or 31.250 kHz), just like 100 Hz or 75 Hz interlace. Because it is derived from the 50 Hz PAL input signal ( $f_{H-PAL}$  = 15.625 kHz) which differs from the NTSC line frequency ( $f_{H-NTSC}$  = 15.750 kHz) the number of lines per frames is slightly different from the standard 525 of the NTSC system. Five 50 Hz input fields (interlace) are converted to six 60 Hz output frames (progressive), five of them having 520 lines and the sixth one 521 lines, see fig. 14. Like the other display mode with unequal field/frame length sequences (100 Hz AABB mode or 75i), it is required to use a DC-coupled deflection stage for the CRT otherwise a vertical jitter can occur.

| For comparison: | vertical<br>frequency | horizontal frequency | lines per<br>field | lines per<br>frame |

|-----------------|-----------------------|----------------------|--------------------|--------------------|

|                 | 50 Hz (int.)          | 15.625 kHz           | 312.5              | 625                |

|                 | 60 Hz (pro.)          | 31.250 kHz           |                    | 520 or 521*        |

|                 |                       |                      |                    |                    |

<sup>\*</sup> every 6th frame has one line less

Fig. 14 Scan conversion from 50 Hz interlace to 60 Hz progressive

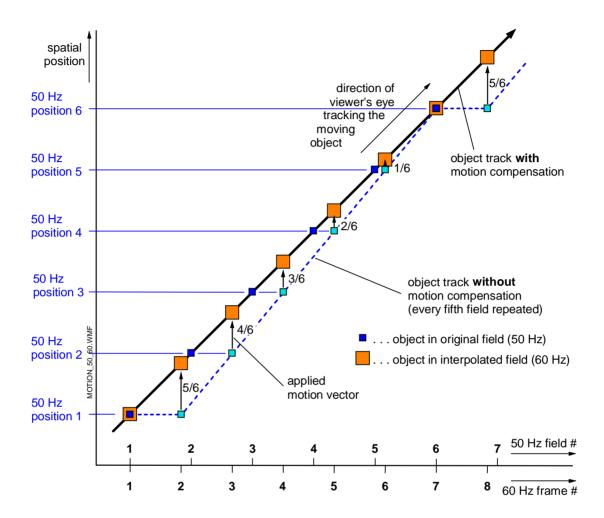

While converting from 50 Hz to 60 Hz basically every 5th 50 Hz field is repeated to get 60 Hz. When watching moving objects these would show a low-frequent and rather annoying judder of 12 Hz. But in this mode also motion compensation is active. Motion vectors are determined and moving objects are shifted toward the position expected by the viewer's eye tracking the moving object, see fig. 15. A suitable fraction of the vector is applied depending on the current phase between the 50 Hz input and the 60 Hz output signal.

Fig. 15 Motion compensation in 50i/60p conversion mode

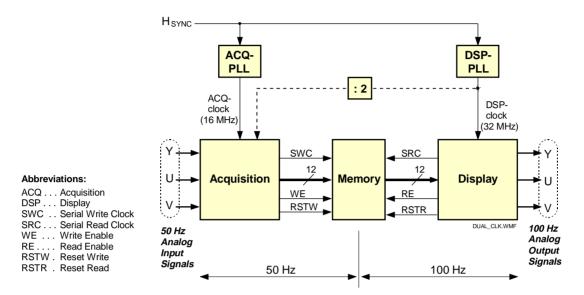

#### 3.12 Double clock system

In our scan conversion concepts the display line frequency and system clock are double that of the acquisition side. In a simple approach a PLL could generate the display clock from the input line frequency, with the acquisition clock being just derived from the display clock by a division of 2. In fig. 16 this is shown by the dotted line.

This approach has the disadvantage that an unstable horizontal sync pulse as it is generated for example by a VCR (especially during head change) will influence both the acquisition clock and the display clock. An improvement is to use two PLLs and to optimize each one separately: the acquisition PLL is to be made fast, so it can easily follow any time base changes of the input sync; the display PLL is to be made slow in order to generate a stable display.

The SAA4979 has the display PLL integrated onto the chip. The horizontal reference pulses are taken from the ITU data stream. The acquisition PLL is located in the color decoder (SAA7114/..15/..18).

Fig. 16 Single clock and dual clock system in scan conversion

# Application Note AN10233

#### 4. Functional description of the SAA4979

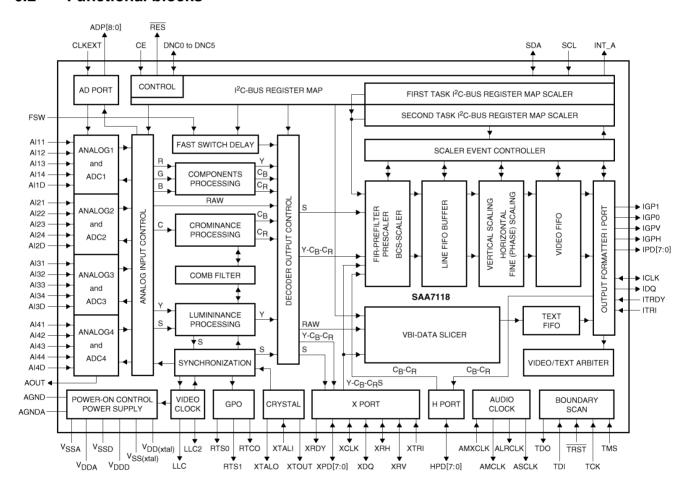

The SAA4979 is a stand-alone IC for 4:2:2 video scan conversion. Conversion can either be field rate doubling from 50/60 Hz to 100/120 Hz or conversion to progressive scan. The main characteristic is that all digital functions including a 3.5 MBit field memory are placed inside one IC.

The IC supports two digital ITU-656 video input data streams to allow picture-in-picture processing. It provides picture improvement features and non-linear horizontal picture compression or expansion and has analog YUV outputs for a display. The on-chip memory is used for scan conversion as well as for field-based noise reduction. Various video enhancing features are provided which are controlled by the embedded 80C51 microprocessor core. An I<sup>2</sup>C bus interface offers communication with an external master controller.

The SAA4979 is designed especially for an economy 100 Hz application and allows a one-chip 100 Hz concept. It is the successor of the SAA4977. For mid- and high-end applications it offers an expansion port for vector based motion estimation and compensation ICs like the SAA4992/3/4 (FALCONIC) or the SAA4998 (FALCONIC-EM). Besides motion-compensated field rate up-conversion, these ICs offer de-interlacing, noise reduction and zoom.

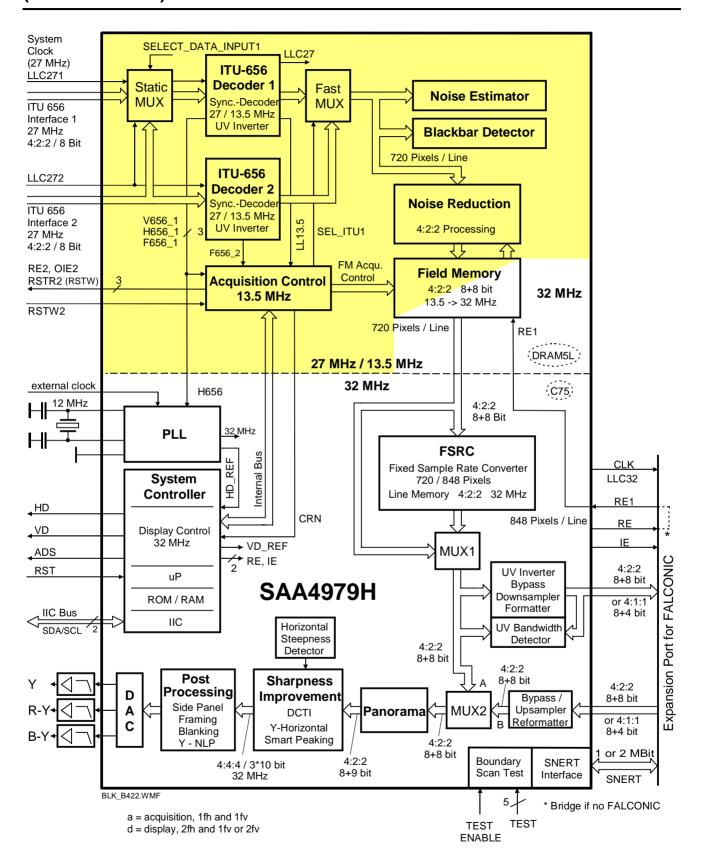

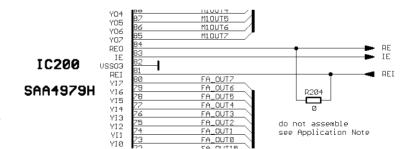

The functional block diagram of the SAA4979 is shown in fig. 17. The IC is made up of two chips (multi-chip module, MCM). The horizontal dashed line marks the border between the two dies: the upper part contains the front end processing and the 3.5 MBit embedded DRAM for field storage. The lower part contains further signal processing and the backend of the IC. The shaded area marks the part which runs with basic line and field frequencies and a clock of 27 MHz for the ITU656 coded input signals. The non-shaded part runs with double line and field frequency and a clock of 32 MHz. Throughout the IC signal processing in the 4:2:2 format is performed.

#### 4.1 Digital processing at 1f<sub>H</sub> level

#### 4.1.1 ITU-656 decoder

The SAA4979H is equipped with two digital inputs for 8 bit wide Y/UV signals in the 4:2:2 format complying to the ITU-656 standard. There are two separate decoders with equal functions. Decoder 1 gets the main input signal and decoder 2 gets the second signal, so two signal sources can be displayed on the screen at the same time, e.g. as DW (double window), PIP (picture-in-picture) or POP (picture-outside-picture, on a side panel).

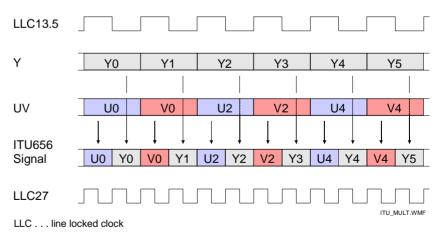

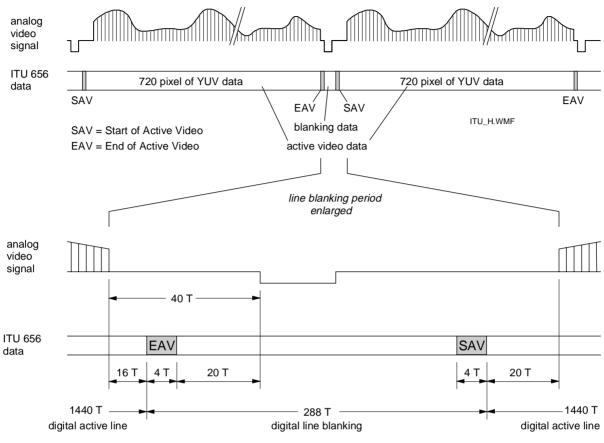

Data is input at 27 MHz with Y and U/V samples alternating in the following order: U0 - Y0 - V0 - Y1 - ..., see also fig. 18. 720 pixels are processed per active video line with timing reference codes being inserted at the beginning and end of each line. A 'Start of Active Video' (SAV) code is generated before the first active video sample and a 'End of Active Video' (EAV) code after the last active video sample, see fig. 19 where the position of horizontal

Fig. 18 ITU-656 multiplex signal

timing reference codes is depicted.

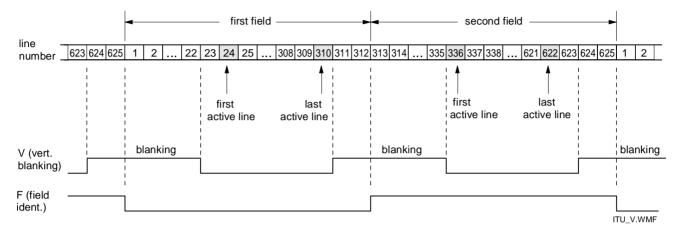

The active video data words are limited to 1 to 254, since the data words  $00_H$  and  $FF_H$  are used for identification of the timing reference codes. These codes are packets of four data words with the first three being  $FF_H$  - 00 - 00. The fourth word has bits identifying the beginning and end of horizontal and vertical blanking as well as the first and second field. An overview of the video timing reference codes is given in fig. 20.

Fig. 17 Block diagram of the SAA4979H

# Application Note AN10233

LLC27 = 27 MHzT = 1/LLC27 = 37 ns

digital line = digital line blanking + digial active video = 1728T

Fig. 19 ITU-656 horizontal timing

| Data bit<br>number | First<br>word<br>(FF) | Second<br>word<br>(00) | Third<br>word<br>(00) | Fourth<br>word<br>(xy) |   |  |  |  |  |  |

|--------------------|-----------------------|------------------------|-----------------------|------------------------|---|--|--|--|--|--|

| 7 (MSB)            | 1                     | 0                      | 0                     | 1                      |   |  |  |  |  |  |

| 6                  | 1                     | 0                      | 0                     | F                      |   |  |  |  |  |  |

| 5                  | 1                     | 0                      | 0                     | V                      |   |  |  |  |  |  |

| 4                  | 1                     | 0                      | 0                     | 0                      | Н |  |  |  |  |  |

| 3                  | 1                     | 0 0                    | 0                     | P <sub>3</sub>         |   |  |  |  |  |  |

| 2                  | 1                     | 0                      | 0                     | P <sub>2</sub>         |   |  |  |  |  |  |

| 1                  | 1                     | 0                      | 0                     | P <sub>1</sub>         |   |  |  |  |  |  |

| 0 (LSB)            | 1                     | 0                      | 0                     | P <sub>0</sub>         |   |  |  |  |  |  |

| ITU_CODE.WMF       |                       |                        |                       |                        |   |  |  |  |  |  |

F = 0 during field 1

= 1 during field 2

V = 0 elsewhere

= 1 during field blanking

H = 0 in SAV (Start of Active Video)

= 1 in EAV (End of Active Video)

$P_0 \dots P_3$ : protection bits for 1-error correction and 2-error detection

Fig. 20 ITU-656 timing reference codes

While bit H in the fourth code word denotes the beginning and end of the active video line, bit V defines the beginning and end of vertical blanking and bit F serves for identifying first and second field. The lines numbers where these bits change are given in fig. Fig. 21.

Fig. 21 ITU-656 vertical timing

#### 4.1.2 Inputs

There are two inputs for digital video data and two ITU-656 decoders. Each 8-bit wide data channel has its own 27 MHz line-locked clock LLC27. One of these inputs can be selected for the ITU-656 DECODER 1 by the STATIC MUX in front of it. Alternatively both inputs can be fed to both ITU-656 decoders and the signals are combined by the FAST MUX to a double window or to a picture-in-picture (PIP) image. Only decoder 1 provides pulses for vertical, field, horizontal and clock synchronization to the ACQUISITION CONTROL block and to the PLL while decoder 2 delivers only field phase information.

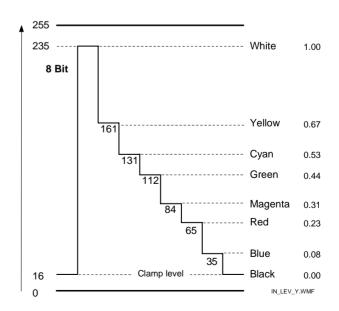

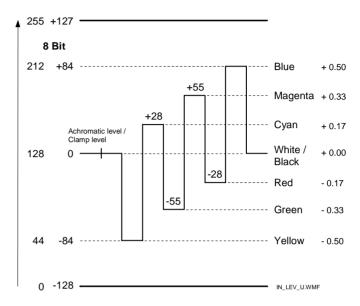

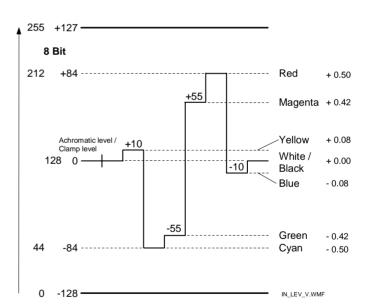

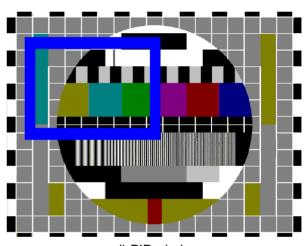

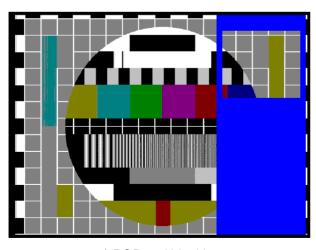

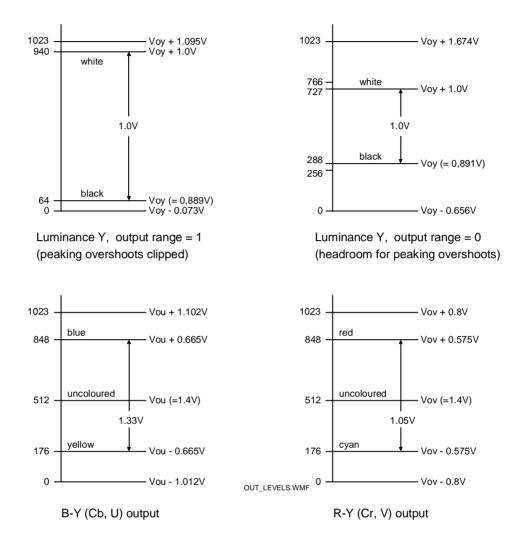

Fig. 22 Digital levels of Y input signal for color bar 100/0/75/0 (ITU-601)

The levels of the input signal components Y, Cr, Cb ("YUV") are depicted in fig. 22, 23, and 24, the right most scale is normalized to the amplitude 1.

Fig. 23 Digital levels of U input signal for color bar 100/0/75/0 (ITU-601)

Fig. 24 Digital levels of V input signal for color bar 100/0/75/0 (ITU-601)

#### 4.1.3 Double window and picture-in-picture processing

Data from the subchannel can be inserted into the data stream of the main channel by means of a fast switch. The two channels can be used together with one or two external field memories to implement e.g. double window or picture-in-picture (PIP) processing. In case of PIP processing the second input has to be scaled to the desired size, in case of double window also the main input has to be scaled. This scaling has to be done in front of the SAA4979, e. g. in the color decoder or special buffer memories which in case of PIP are also needed for synchronization. This synchronization of the subchannel to the main channel is achieved by providing synchronized read signals (RE2 and RSTR2) for the external field memories, whereas the write signals need to be provided together with the incoming data by the external signal source. Both field based and frame based PIP processing is supported. Also a multi-PIP mode is possible by freezing the data in the internal field memory within certain areas via the programmable internal control signal IEint.

#### 4.1.4 Black bar detector

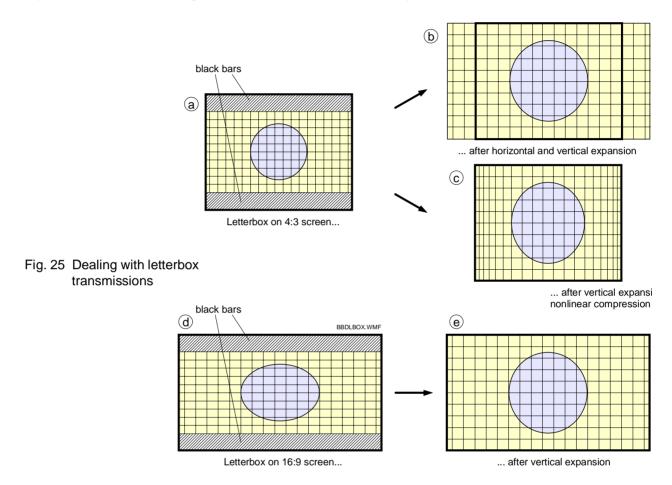

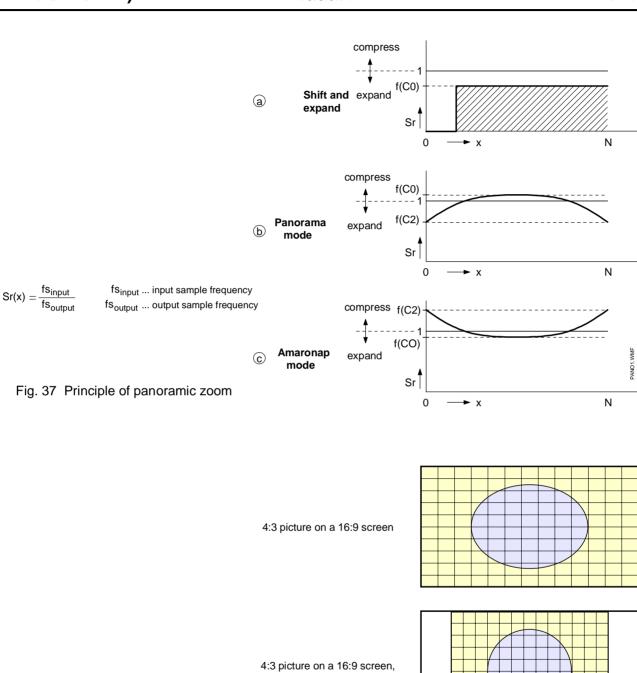

Wide screen transmissions ("letterbox format") displayed on a conventional 4:3 screen will result in black bars at the top and bottom, see ⓐ in fig. 25. If no measures are taken, they will also leave these black bars on a wide

16:9 screen, see (d) in fig. 25. On a 4:3 screen this is acceptable because the proper aspect ratio is maintained. On a 16:9 screen it appears distorted however, which is less acceptable. In fig. 25 some measures are pointed out of what to do with a letterbox signal.

On a 4:3 display the picture can be expanded horizontally and vertically to fill the whole screen, this results in some parts of the picture getting lost (left and right side, see part (b) in fig. 25). Another way is to expand the picture vertically and activate the inverse panorama mode ("amaronap mode") which compresses the left and right side so everything fits on the screen (c) in fig. 25).

On a 16:9 screen the only desirable action would be to expand the picture vertically. This would fill the whole screen and restore a proper aspect ratio (e) in fig. 25).

When there is no information transmitted about the picture format, the display has to be adjusted manually. An automatic mode though becomes available if the blackbar detection of the SAA4979 is activated and its results are evaluated.

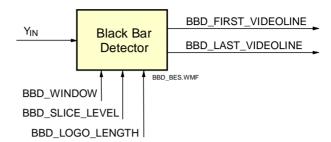

Fig. 26 shows the block diagram of the black bar detection. All measurements are done in a rectangular window which is defined by the four parameters *BBD\_HSTART*, *BBD\_HSTOP*, *BBD\_VSTART*, and *BBD\_VSTOP*. The horizontal start and stop position can be programmed in steps of 4 pixels, the vertical position in steps of one line.

# Application Note AN10233

Fig. 26 Block diagram of the black bar detection

The aim of the black bar detector is to determine the first and last non-black line in the picture. At the beginning of a field a temporary register *first\_videoline* is incremented every line as long as the line is found to be black. The incrementing stops with the first non-black line. This one represents the top of the letterbox picture. The register content can be read as *BBD\_1ST\_VIDEOLINE*. The bottom of the letterbox picture is found in a similar way. Incrementing of the temporary register *last\_videoline* stops with the last non-black line, and the register content can be read as *BBD\_LAST\_VIDEOLINE*. *BBD\_1ST\_VIDEOLINE* is a 7-bit value and *BBD\_LAST\_VIDEOLINE* is an 9-bit value. Both read registers of the black bar detector can be read by the internal microprocessor only. They are evaluated and the result is available in the read register 09<sub>H</sub>.

Recognizing a black line can be influenced not only by adjusting the window borders, but also by two more parameters. *BBD\_SLICE\_LEVEL* determines whether a pixel is considered black or not and *BBD\_EVENT\_VALUE* sets a limit on how many non-black pixels are allowed while that line is still considered to be black. Both parameters are entered as 6-bit values which are internally multiplied by 2 to get the actual slicing level or event number.

#### 4.1.5 Dynamic noise reduction

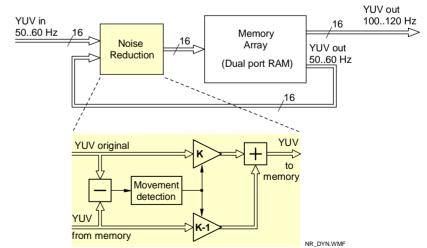

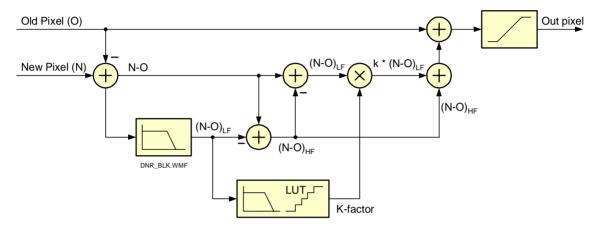

The dynamic noise reduction circuit in the SAA4979 is based on a recursive signal filtering in which an actual and a previous (field delayed) signal are mixed. The level of the noise reduction is dynamically controlled depending on movement, i. e. depending on differences between pictures. The circuit therefore is closely related to the IC's field memory. This memory has two output ports: one is used for double scan rate and the second one is a 50/60 Hz output and is used for the noise reduction loop. Fig. 27 shows the block diagram of the noise reduction circuit. A more detailed diagram can be found in the data sheet of the SAA4979<sup>1</sup>.

Fig. 27 Basic block diagram of the DNR circuit

Noise reduction can be activated by forcing the *NREN* control bit to HIGH. The amount of noise reduction is controlled by the k-factor. K determines the part of fresh video information and is between 0 and 1. A low value of k

<sup>1.</sup> SAA4979H: Philips Semiconductors data sheet

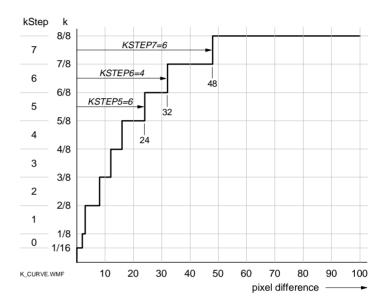

means a high amount of recursion (and thus high noise reduction) while for k = 1 noise reduction is turned off. In 'fixed k mode' the value of k is defined by the register bits *KLUMAFIX* and *KCHROMAFIX* while in adaptive mode k is controlled by the amount of motion found. Motion is determined by the local (low pass filtered) difference between the original and the field delayed picture. Except for settings like k = 1 (noise reduction off) or k = 0 (frozen picture) a fixed k-factor is not recommended since it results in wiping or smearing of moving objects. The dependency of the k-factor from the detected motion is defined in the k-curve which is programmed by the register settings *KSTEPO* .. *KSTEP7*. Fig. 28 shows a sample k-curve. In this curve the dependency of the k-

Fig. 28 Sample noise reduction k-curve

factor on the pixel difference between new and old pixel is defined. When programming the curve the different weights of the *KSTEP* values have to be observed. In fig. 28 three examples are shown: *KSTEP6* and *KSTEP7* have the weight of 8, so *KSTEP6* = 4 and *KSTEP7* = 6 gives k-values of 32 and 48 resp., while *KSTEP5* = 6 with a weight of 4 gives 24. A complete overview of kStep, k, and related weight is given in fig. 29.

| kStep  | k =      | weight |

|--------|----------|--------|

| kStep0 | 1/16 1/8 | 1      |

| kStep1 | 1/8 2/8  | 1      |

| kStep2 | 2/8 3/8  | 2      |

| kStep3 | 3/8 4/8  | 2      |

| kStep4 | 4/8 5/8  | 4      |

| kStep5 | 5/8 6/8  | 4      |

| kStep6 | 6/8 7/8  | 8      |

| kStep7 | 7/8 8/8  | 8      |

Fig. 29 Defining a k-curve

The effective noise reduction is furthermore influenced by the gain settings *YADAPT\_GAIN* and *CADAPT\_GAIN* which reduce or amplify the measured pixel differences before they are used for the k-curve look-up table. Varying these register settings from 0 to 7 will give a gain setting of 1/8, 1/4, 1/2, 1, 2, 4, 8 and 12.

The calculation of k is done in both the luminance and the chrominance channel, so the amount of averaging can be defined independently for both channels. However the chrominance averaging can also be slaved to the luminance averaging by setting parameter KLUMATOCHROMA = 1. This for example results in an effective decrease of cross color patterns where differences from field to field are only present in the chrominance channel due to the alternating color phase.

A switchable band split filter gives the opportunity to reduce noise only in the lower half of the video spectrum, the upper band remains unchanged. This results in better picture performance without "smearing", particularly at strong settings of other parameters. *UNFILTERED* = 1 turns this filter off.

The required calculations in the recursion loop have only limited accuracy. Remaining errors thus can circulate in the loop without being further reduced. At sudden scene changes this can lead to so-called 'left over images',

faintly visible images of the previous scene. This problem is overcome by turning on the function *NOISESHAPE*. This activates an additional algorithm which eliminates the 'left over image' problem.

#### 4.1.6 Noise estimator

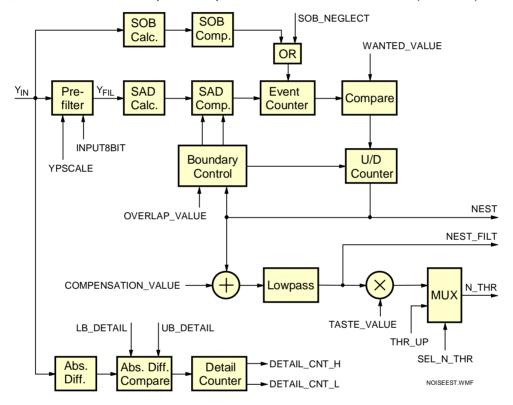

Measuring noise in a video signal would preferably be done in a part without picture content like the vertical or horizontal blanking period. However, measurement here is not reliable because of possible artificial signal content, e. g. new blanking insertion at VCR playback. So in the SAA4979 noise measurement is carried out within the active video signal. Because noise is hard to detect in moving parts of a picture with a high degree of detail information, the task is to find those parts of a picture that have almost no detail (flat areas).

Fig. 30 Block diagram of noise estimator

A block diagram of the noise estimator is given in fig. 30. In the PREFILTER block the interesting part of the spectrum is boosted in order to increase the sensitivity of the noise measurement circuit for video sequences with low noise level. With  $Y_{FIL}$  being the output signal of the filter, parameter YPSCALE has the following influence:

```

\begin{array}{ll} \textit{YPSCALE} = 0: & \textit{scale} = 1 \\ \textit{YPSCALE} = 1: & \textit{scale} = 1/2 \\ \textit{YPSCALE} = 2: & \textit{scale} = 1/4 \\ \textit{YPSCALE} = 3: & \textit{Y}_{\text{FIL}} = \textit{Y}_{\text{IN}} \end{array} \tag{Filter off}

```

The idea of the noise estimator is to find flat areas in the picture and to determine the noise there. In order to find these areas each pixel is compared in amplitude to its neighboring pixels. In the block SAD calculation (SAD = Sum of Absolute Difference) the absolute values of the differences between the actual prefilter output  $Y_{FIL}$  and the four previous ones are summed up. These sums are then compared to a lower and upper bound. Each sum within these limits increments the event counter.

# Application Note AN10233

The event counter can be disabled depending on the result of the SOB (SOB = sum over block) calculation and comparison. This function permits to detect black (level below a lower clipping level *Iclip*) or white areas (level above an upper clipping level *uclip*) in the picture (e. g. black bars or side panels) which may have a signal content not representative for the picture. The interval between *Iclip* and *uclip* can be varied by the control parameter *CLIP\_OFFSET*, see fig. 31. Parameter *SOB\_NEGLECT* = 1 means that the result of the SOB comparison is not used and noise measurement is carried out in the complete video range, *SOB\_NEGLECT* = 0 turns off measurement around the white and black level.

| clip_offset | real offset | lclip | uclip |

|-------------|-------------|-------|-------|

| 0           | 1           | 17    | 238   |

| 1           | 2           | 18    | 237   |

| 2           | 4           | 20    | 235   |

| 3           | 8           | 24    | 231   |

Fig. 31 Clipping levels in the SOB calculation

At the end of every field the value of the event counter is stored and the counter is reset. The stored number of events is compared to the user defined *WANTED\_VALUE*. If the number of events is smaller than *WANTED\_VALUE* then a 4-bit up/down counter is incremented, otherwise it is decremented. The contents of the up/down counter is the noise estimator value *NEST* and can be read by the microprocessor. It is also used as input to the boundary control block where the lower and upper limits for the SAD comparison are adjusted. In this way the control loop is closed and the sensitivity can be influenced by *WANTED\_VALUE*. The lower and upper limits are furthermore adjusted by the parameter *GAIN\_UPBND* which determines the difference between these two limits, see fig. 32.

| GAIN_UPBND | lobnd_del | upbnd                  |

|------------|-----------|------------------------|

| 0          | 015       | 1.5 * lobnd + 1        |

| 16         | 015       | lobnd * GAIN_UPBND + 1 |

| 7          | 03        | 1.5 * lobnd + 1        |

| 7          | 415       | lobnd * (0.5 * lobnd)  |

lobnd\_del... lower boundary of previous fieldupbnd... upper boundaryGAIN\_UPBND... control input for calculating upbnd

Fig. 32 Calculation of the interval upper boundary *upbnd*

It is difficult to avoid that scenes with a large amount of detail result in a higher noise estimate compared with a scene of less detail but the same amount of noise. Therefore a function to measure the detail is incorporated. The difference between every two adjacent pixels is taken and compared to  $LB\_DETAIL$  and  $UPB\_DETAIL$ . The number of times in a picture where this difference falls in between these boundaries is counted and can be read by the microprocessor in a two byte value:  $DETAIL\_CNT\_H$  and  $DETAIL\_CNT\_L$ . The microprocessor evaluates these data and calculates a correction factor  $COMPENSATION\_VALUE$  for the noise estimation.

The noise estimate *NEST* is also available in a lowpass filtered version: *NEST\_FILT*. After a possible compensation offset a lowpass filter generates a moving average over the last 16 *NEST* values. The filter is recursive and generates a 13 bit value which is scaled back to 8 bits for output as *NEST\_FILT*.

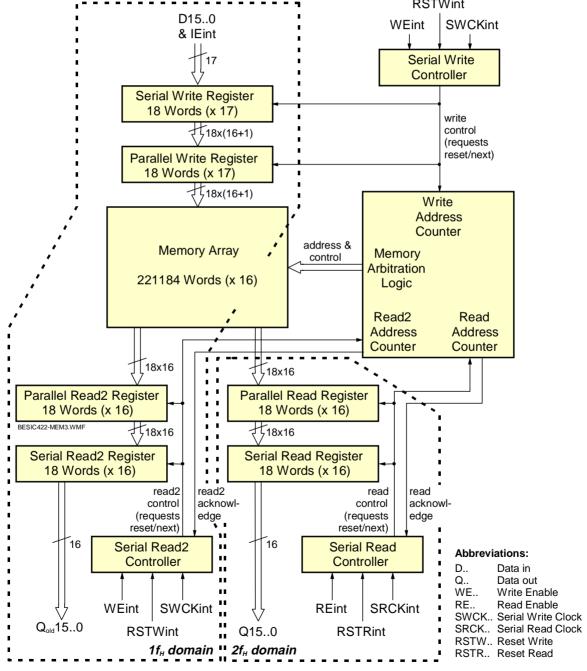

#### 4.2 3.5 MBit field memory

The SAA4979 has a built-in scan conversion memory. The memory is similar to the SAA4956. The main difference is its data width of 16 bits instead of 12, so now video data in 4:2:2 format can be processed. The field memory is capable to store for example up to 307 video lines of 720 pixels in 4:2:2 format. It has one write interface (controller and registers) to store  $1f_H$  data and two read interfaces, one to read field delayed  $1f_H$  data for the

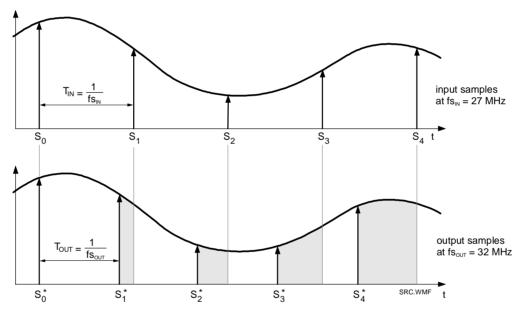

noise reduction function and the other to read  $2f_H$  data for the following data processing, see noise reduction block diagram in fig. 27. Since two asynchronous clock domains are involved (SWCK<sub>int</sub> as  $1f_H$  clock and SRCK<sub>int</sub> as  $2f_H$  clock) the read and write access to the memory array is controlled asynchronously by the memory arbitration logic triggered via request and acknowledge pulses.